使用FPGA构建的数字滤波器设计方案

在Matlab/Simulink环境下,采用DSP Builder模块搭建FIR模型,根据FDATool工具对FIR滤波器进行了设计,然后进行系统级仿真和ModelSim功能仿真,其仿真结果表明其数字滤波器的滤波效果良好。通过SignalCompiler把模型转换成VHDL语言加入到FPGA的硬件设计中,从QuartusⅡ软件中的虚拟逻辑分析工具SignalTapⅡ中得到数字滤波器实时的结果波形图,结果符合预期。

0 引言

在信息信号处理过程中,数字滤波器是信号处理中使用最广泛的一种方法。通过滤波运算,将一组输入数据序列转变为另一组输出数据序列,从而实现时域或频域中信号属性的改变。常用的数字滤波器可分为有限脉冲响应(FIR)滤波器和无限脉冲响应(IIR)滤波器两种。其中,FIR数字滤波器具有严格的线性相位,而且非递归结构也保证了运算的稳定性。在实时性要求比较高的应用场合,采用可编程芯片FPGA加以实现,相比于DSP芯片或专用芯片的实现方法,具有高速、高精度、高灵活性的优点。本文在采取了一种基于FPGA和DSP Builder的方法设计FIR数字滤波器时,采用了层次化、模块化的设计思想,遵循DSP Builder的设计开发流程,在Matlab/Simulink 中建立模型并进行系统级仿真,再进行Verilog语言转换,ModelSim仿真验证无误后实现了FIR数字滤波器的实时测试。

1 FIR 数字滤波器的基本原理及结构

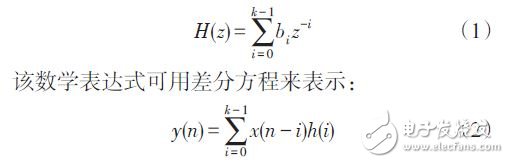

对于一个FIR滤波器系统,它的冲击响应总是有限长的,其系统函数可以记为:

式中:x(n) 是输入采样序列;h(i) 是滤波器系数;k 是滤波器阶数;y(n) 表示滤波器的输出序列。

图1为k 阶FIR数字滤波器的结构框图。

2 FIR 数字滤波器的设计流程

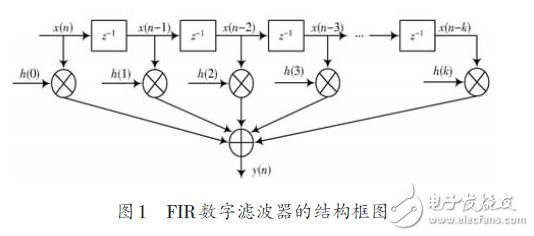

该设计流程主要涉及到Matlab/Simulink、DSPBuilder和Quartus Ⅱ等工具软件的开发设计。整个设计流程,包括从系统描述直至硬件实现,可以在一个完整的设计环境中完成,如图2所示。

(1)Matlab/Simulink 中设计输入,即在Matlab 的Simulink环境中建立一个扩展名为mdl的模型文件,用图形方式调用Altera DSP Builder 和其他Simulink库中的图形模块(Block),构成系统级或算法级设计框图(或称Simulink设计模型)。

(2)利用Simulink的图形化仿真、分析功能,分析此设计模型的正确性,完成模型仿真,也叫系统级仿真。

(3)DSP Builder设计实现的关键一步,通过Signal-Compiler把Simulink的模型文件转化成通用的硬件描述语言Verilog文件。

(4)转换好的Verilog源代码用ModelSim软件进行功能仿真,验证Verilog文件的正确性。接下来的几个步骤是对以上设计产生的Verilog的RTL代码和仿真文件在Quartus Ⅱ工具软件中进行综合、编译适配,生成扩展名为。sof的文件加载到FPGA硬件系统中。

3 FIR 数字滤波器的详细设计

3.1 FIR数字滤波器模块设计与系统级仿真

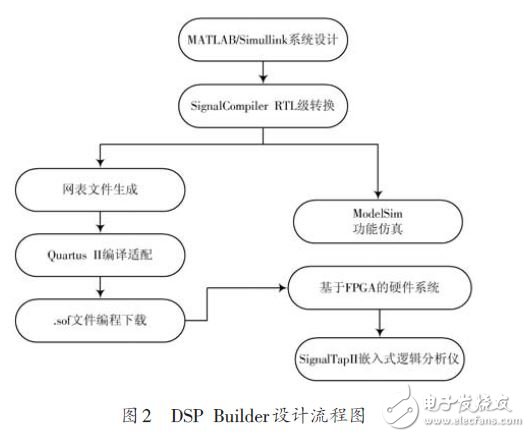

根据FIR数字滤波器的原理,在Simulink环境下搭建16阶的FIR数字滤波器结构,如图3所示。

在模型的搭建过程中,使用了两个8位的Shift Taps移位寄存器模块对输入信号进行分解,然后根据数字滤波器的原理进行算法计算。

模型搭建好之后,需要确定16阶FIR数字滤波器的系数,在这使用Matlab中的FDATool滤波器设计工具来确定。确定好滤波器的指标:

(1)设计一个16阶的FIR 滤波器;

(2)低通滤波器;

(3)采样频率fs为16 384 Hz,截频点频率fs为533 Hz;

(4)输入序列位宽为16位。

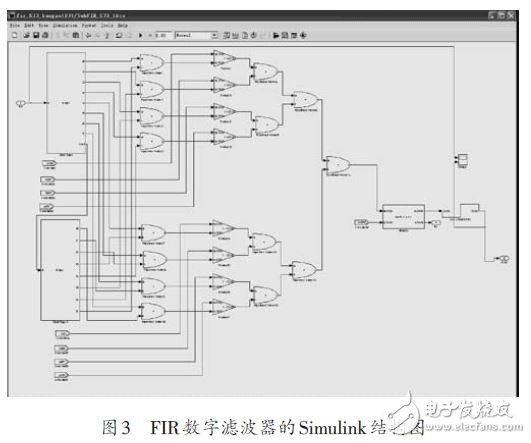

在设计滤波器界面中,如图4所示,进行下列选择:

(1)滤波器类型(Filter Type)为低通(Lowpass);

(2)设计方法(Design Method)为FIR,采用窗口法(Window);

(3)滤波器阶数(Filter Order)定制为15(设置为15 阶而不是16阶,是由于设计的16阶FIR滤波器的常系数项h(0)=0);

(4)滤波器窗口类型为Kaiser,Beta为0.5.

所有的选项确定好后,在FDATool滤波器设计界面中点击"Design Filter",Matlab就会计算滤波器系数并作相关分析。图5所示为滤波器的幅频响应,图6所示为滤波器的阶跃响应。

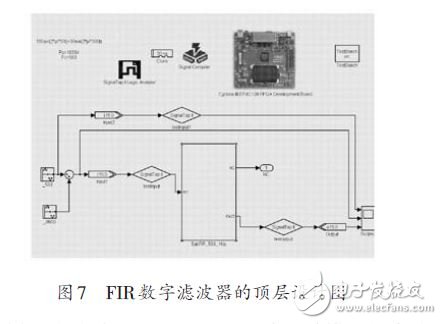

由于所有的模块都在同一个Simulink图中,这时的Simulink设计图显得很复杂,不利于阅读和排错,因此把FIR数字滤波器模型做成一个子系统在设计图中显示出来,如图7所示,这就是Matlab中的层次化设计,在顶层设计图中,滤波器作为名称是SubFIR_533_16js的一个模块出现。同时,图7中还设置了其他模块,包括仿真信号输入模块、Signal Tap Ⅱ信号实时监测模块、Signal Compiler模块、硬件开发板模块、TestBench模块。

这样整个滤波器的Simulink电路设计模型

- 基于FPGA的IIR数字带通滤波器的设计方案及实现(02-13)

- 非常详细的滤波器基础知识简介(03-07)

- 详解FIR滤波器和IIR滤波器区别(04-04)

- 常用的Σ-Δ ADC数字滤波器类型(05-09)

- 一种基于混合信号技术的汽车电子单芯片设计(04-08)

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)