导入栅极屏蔽结构 沟槽式MOSFET功耗锐减

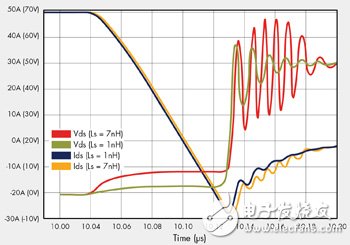

电感,为电路必然现象。封装的电感大部分源于接脚长度,业界标准的通孔TO-220封装通常会有7nH的接脚电感,但 PQFN56 SMD封装却仅有1nH。另外还有电路Layout产生的寄生电感和电容。在电路Layout中,线间距1公分约会产生6?10nH的电感。这些寄生电感直接影响到体二极体的反向恢复特性和电压突波峰值。在资料表中的体二极体恢复电荷是COSS位移电流之总和,包括回收的少数载流子的电流,以及从测试电路的公共源极电感产生的反应电流。图2所示为根据各种常见源极电感模拟之体二极体反向恢复过程波形;很明显地,较高的电感将导致较大的Qrr和更高的峰值电压。若是使用1nH源极电感之Power56 SMD封装,峰值电压将可从59.2V降低到55.6V。因此,如何尽量减少源极电感,成为改善系统效率的主要关键。

图2 根据源极电感得出之体二极体的反向恢复波形比较

栅极屏蔽MOSFET性能跃进

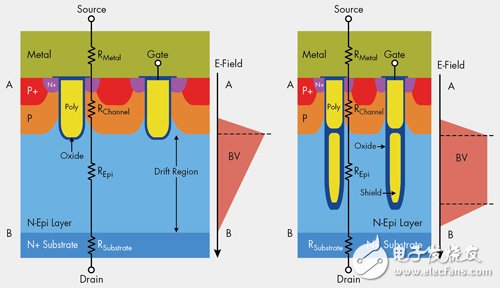

现今厂商已开发出许多新技术,可提高RDS(ON)×QG FOM,其中主要针对导通阻抗中电压MOSFET(BVDSS

图3 传统沟槽栅极MOSFET(左)与采用屏蔽栅极技术的沟槽MOSFET(右)之垂直结构

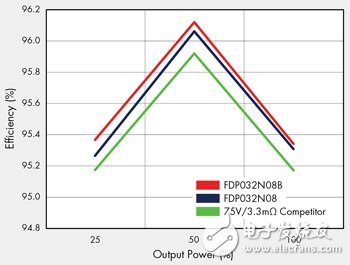

由于轻负载时的效率日益重要,栅极驱动损耗与缓冲器损耗也变得更加重要。因此,低QSYNC与高软度的体二极体成为改善同步整流效率的重要因素。然而,RDS(on)仍是应用中的关键参数。图4显示表1中三个元件在600W相移式(Phase-shifted)全桥转换器同步整流系统的效率比较。在轻负载条件下,使用最新栅极屏蔽沟槽MOSFET的系统总效率为95.36%,在全负荷状态下则是95.34%。由于低驱动损耗和关断切换损耗,在10% 的负载下采用栅极屏蔽架构的MOSFET系统总效率,相较于传统沟槽栅极MOSFET和75V/3.3mOhm对照组,分别高出0.1%和0.19%。从图4效率比较结果明显可知,栅极屏蔽沟槽MOSFET在全负荷和轻负荷条件下,都能显著减少功率损耗,并结合小QSYNC和快速切换的软反向恢复体二极体性能,可以大大提高同步整流效率。

图4 在600W时的同步整流效率比较

(本文作者Won-suk Choi/Dong-wook Kim/Dong-kook Son皆任职于快捷半导体)

- 凌力尔特大功率多相同步升压型DC/DC控制器LTC3787(10-15)

- 一种200V/100A VDMOS 器件开发(02-23)

- 电动自行车控制器MOSFET驱动电路的设计(11-18)

- 两种常见的MOSFET驱动电路设计(12-02)

- 集成MOSFET 的分立器件方案(01-30)

- 功率MOSFET的锂电池保护电路设计(04-18)