基于DSP的双通道数字存储示波器

波卡的电源主要分三部分,一部分给高速A/D转换器供电,第二部分给FPGA供电,第三部分是给DSP芯片供电。考虑到成本和实用性等因素,使用比较常见的可调电源LM1117为A/D转换器和FPGA供电。

A/D转换器需要的额定供电电压是+3.3V,单片A/D转换器在正常工作的情况下的功率是 689mV,故耗费的电流在210mA左右,LM1117的额定供电电流800mA,使用两片可较好满足要求。FPGA供电分为内核供电和IO端口供电。内核供电电压为1.2V,由LM1117供电;IO端口可以进行包括1.5V、1.8V、2.5V、3.0V和3.3V等多种配置,其电源也同样由 LM1117来提供。示波卡的运算放大器和场效应管等器件所需的负电压则由LM2991来提供。LM2991是输出可调低压差稳压器,输出电压调节范围为 -2V至-25V(输出电流为1A)。

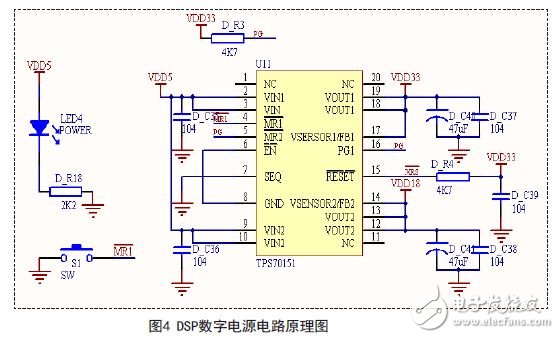

DSP需要工作在更稳定的电压下,在示波卡的设计中用到了由TI公司生产的双电压输出芯片 TPS70151.该芯片可以同时提供两路不同的电压,并且可以通过人为控制去改变上电顺序。如图4所示,两路输入VIN1和VIN2都被接到 VDD5,VOUT1和VOUT2输出3.3V和1.8V.SEQ可以用来控制上电顺序,接地说明被置为低电平,那么VOUT1先输出3.3V,直到 VOUT1输出电压达到2.7V左右时,VOUT2才开始有输出电压。MR1和MR2被用来人为的设置输入电压1和输入电压2,可用于控制RESET的输出电平,当两个引脚的任何一个输入电平为低时,那么RESET输出低电平。其他的控制端与DSP芯片连接,那么我们可以通过在DSP中编写C语言程序的方式达到对电源电压的控制。

2.4 LCD显示的设计

在本设计中,采用的LCD是FY43-4827-65K,具有480*272的高分辨率的彩色 TFT显示屏。采用16位标准8080总线接口方式、色彩支持65536色使图像。超高的24MHz无等待总线读写速度,单点读写周期高达42ns,无需任何等待,可以和任何高速系统接口。独有显存更新窗口设定功能,用户可任意指定读写区域。

对缓冲区的较高要求,示波卡需要对系统内存进行扩展,所以加入SDRAM作为显示缓冲区,用于存储临时数据、中间结果。

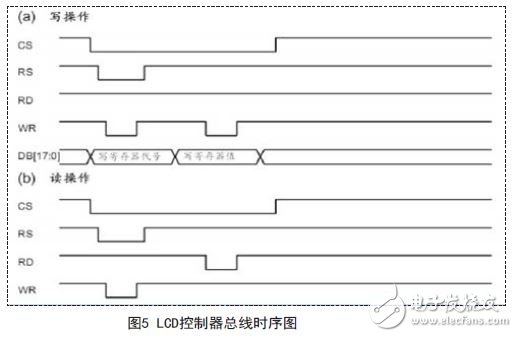

LCD以ILI9320为控制器,ILI9230具有统一的时序逻辑(如图5所示)和非常丰富的指令编码,支持MSP430、51、DSP、FPGA等系列CPU.根据LCD控制器中不同的指令编码和DSP中的数据端口定义,还可以自行设计对LCD的控制指令和编程方式,实现对LCD屏上显示位置、显示内容以及色彩的组合控制。

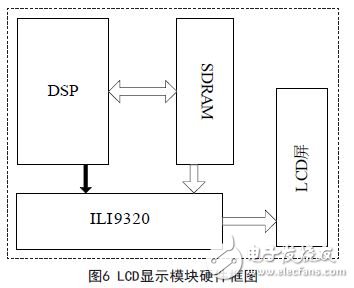

如图6所示,DSP通过数据总线与SDRAM的数据交换,把处理后的数据送入显示缓冲区中。同时DSP也可以通过控制总线向ILI9230发送指令,使其从SDRAM中读取数据,并送入LCD显示,这样就完成了一个显示的过程。

3.结束语

本文采用DSP与FPGA相互配合的方案,设计出了一种嵌入式数字存储示波器。在无操作系统的情况下,实现波形处理和显示以及键盘控制,提高了CPU的运行效率。在本方案中,FPGA作为前端的电路逻辑控制的核心,并做前期的一些数据处理;而DSP做作为本设计中整个系统的核心,示波器的滤波、差值过程以及显示和控制功能均在DSP芯片上完成,数字存储示波器的实时反映速度得到提高。通过实际的测试和使用,该示波器已基本达到了初期的设计要求,各项性能也达到了预定指标。

- 德州仪器基于SN761633的FM收音机解决方案(07-02)

- 基于DS125BR800A的SAS-3协议中继器解决方案(07-01)

- 基于TPA6132A2正相单端放大器电路设计(08-05)

- 由浅入深,蓝牙4.0/BLE协议栈开发攻略大全(5)(08-02)

- 主流ZigBee芯片大盘点(2):德州仪器 CC2530(07-20)

- 由浅入深,蓝牙4.0/BLE协议栈开发攻略大全(3)(07-22)