为ASIC和SoC设计实现最佳化嵌入式存储器

DRAM巨集均为硬巨集单元,大孝长宽比以及介面的可选空间有限。

有一种单电晶体SRAM的特殊变体,采用了可通过标准CMOS制程的架构,因此,它不但不必需修改光罩,也无需额外的制程步骤。此类IP巨集模组具有更高的成本效益(制程成本可节省15-20%),而且可在任何晶圆厂进行加工,也可出于成本或生产能力等塬因,改变制造厂。这种解决方案提供了多种尺寸、长宽比和介面,可逐一指定相应的存储器编译器。对于系统的其余部份来说,产生的存储器模组介面看起来就像静态RAM,但其密度(位元/单元空间)是基于6T储存单元的存储器阵列的2倍(经过对作为空间运算一部份的全部支持电路的平均)。对于大型存储器阵列来说,支持电路所需的空间占百分比较小,存储器模组的空间利用率也更高。

存储器编译器工具 嵌入式存储器编译器的职责在于因应特定存储器应用程式的确切需求,量身定做基本的IP存储器巨集单元。若适用範围足够广,编译器可让设计者选择最优架构,自动产生存储器阵列,并精确确定最佳化程式所需的速度、密度、功率、成本、可靠性与大小等因素。透过编译器的自动化作业,可降低非经常性工程成本,并可减少手动阵列最佳化相关的潜在错误。编译器不但可使客户的核心大小、介面以及长宽比均达到最理想数值,而且还可帮助他们大幅地缩短上市时间。作为编译制程的一部份,编译器还可为设计者提供存储器阵列的电气、实体、模拟(Verilog)、BIST/DFT模型以及合成视图。

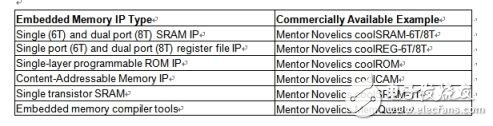

表2:嵌入式存储器IP的商业案例

结论

为新的ASIC/SOC选择最佳嵌入式存储器IP是设计决策的关键。设计者应了解适用于其特定应用程式的最佳存储器特性及其所有关键参数,所寻找的存储器 IP应具有足够的适应性,可满足目标SoC的各种需求。尽管有现成的免费存储器IP可供使用,但与可为特定应用程式提供更好特性的付费IP相较,它并不见得总能提供最佳解决方案。

经过充分除错的存储器IP具有体积小、泄漏功率低、动态能耗低、速度快等特点,可为设计者的解决方案进一步最佳化,不但可在产品的整个寿命周期内,带来上百万美元的营收,同时也使其晶片在竞争激烈的ASIC/SOC市场上,得到更好的差异化。

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)

- 高压电池组监视器可实现先进的电池系统(10-14)

- 如何最大化延长即使具有老化电池的汽车电池组运行时间(08-14)

- 高准确度 60V 电量计如何测量电量?(09-12)

- Cypress电容式触控元件出货量突破10亿颗(08-14)

- 瑞萨电子3大ADAS检测系统解决方案简述(02-08)