为ASIC和SoC设计实现最佳化嵌入式存储器

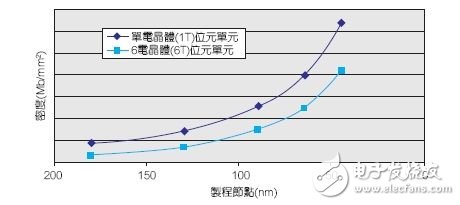

图4所示。与6电晶体(6T)位单元相较,位容量一定时,单电晶体(1T)位单元最多可减少50%的晶片空间。在设计中,对速度要求较低而密度要求较高时,1T 式架构是较为理想的选择。由于可采用批量CMOS制程,省却了额外的光罩环节,因而有益于成本压缩。在高速应用方面,设计者可采用6T甚至8T位单元来满足其速度要求。

图4:存储器密度与不同嵌入式存储器IP架构的关系

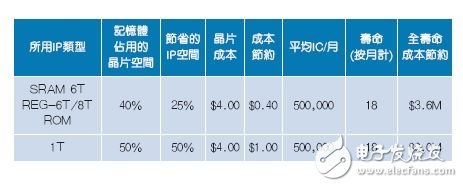

成本 对于SoC/ASIC来说,为了大幅压缩成本,与次优IP(常是免费IP)相较,设计者更喜欢选择‘节省空间’的IP参数。尽管有许多存储器IP参数可供设计者免费选用,但在产品的整体收益性上,却并不见得是最经济的解决方案。在很多情况下,与‘免费’存储器IP相较,透过改善的嵌入式存储器IP密度与性能来压缩制造成本,效果更为显着。

在产品的整个生命周期中,存储器体积最佳化对量产成本的影响如表1所示。在表1中,存储器IP占用的晶片空间以百分比表示。可透过晶片成本、量产效率以及产品寿命,计算高密度存储器的成本压缩效果。节省的IP空间根据图4可看出,1T和6T 存储器的密度增量比值约为2:1。

表1:高密度IP与成本节约

嵌入式存储器IP选用指南

为了了解存储器设计中的选择要件,可针对具有最先进功能的付费嵌入式存储器类型加以归纳:

单埠(6T)和双埠(8T)SRAM IP 由于这类存储器架构大多适用于主流CMOS制造制程,无需额外的制程,因此基于传统6T储存单元的静态RAM存储器模组正成为ASIC/SoC制造中的主流。6T储存单元采用经验证适用于晶圆代工厂生产的高速、低功耗设计6T/8T位单元,是大规模编程或数据存储器模组的理想元件。6T储存单元适用于储存能力从几位元到几兆位元的储存阵列。

根据设计者采用针对高性能还是针对低功耗最佳化的CMOS制程,采用此种结构的储存阵列经过设计后,可满足多种不同的性能需求。经高性能CMOS制程制造的SRAM,在功耗降低的同时,可让40nm和28nm等先进制程节点的存取时间可降低到1ns以下。随着制程节点的进展,外形尺寸的微缩,采用传统6T储存单元建构的静态RAM单元尺寸更小,存取时也间更短。

SRAM存储器单元的静态特性使其可保留最小数目的支持电路,只需要对位址进行解码,并为解码器、感测和计时电路的设计提供讯号即可。

单埠(6T)和双埠(8T)暂存器IP 对于快速处理器缓冲存储器和较小的存储器缓冲(最高约每个巨集72Kbit)来说,这类暂存器存储器组合IP是个不错的选择。暂存器同时具备占用空间最小、性能最快等特点。

单层可编程ROM IP 这种结构功耗和速度均相对较低,特别适用于空间有限的储存、固定数据的储存或体积稳步递增的应用程式储存。这类IP可支持多晶片组和不同长宽比,既缩小了晶片体积,又获得了最佳速度。为加速设计周期,部份IP还提供用以驱动存储器编译器的编程脚本语言。

内容寻址存储器IP 由于速度更快、能耗更低,以及较执行大量搜寻任务的应用程式演算法占用晶片空间更小,这类IP大多作为TCAM(三进制)或BCAM(二进制)IP,用于搜寻引擎类应用程式。在一般情况下,搜寻可在单一时脉周期内完成。TCAM和BCAM常用于封包转发、乙太网路位址过滤、路由查询、韧体搜寻、主机ID搜寻、存储器去耦合、目录压缩、封包分类以及多工高速缓冲存储器控制器等。

单电晶体SRAM 这种结构虽然速度有所降低,但密度极高,适用于180nm、160nm、152nm、130nm、110nm、90nm以及65nm制程。尤其适用于需要大量晶片储存空间、但不需要极高的存取速度的ASIC/SoC程式,以及空间有限且存储器模组存在泄漏电流的设计。该结构可产生与SRAM工作塬理相似的存储器阵列,但其基础为单电晶体/单电容器(1T)储存单元(如动态RAM所用)。

由于采用了6T储存阵列,因此在相同的晶片空间上,单电晶体SRAM阵列的储存能力更强,但必须在系统控制器和逻辑层面了解存储器的动态特性,并在刷新控制方面发挥积极作用。在某些情况下,为了使其看起来像简单易用的SRAM阵列,也可能对DRAM及其自身控制器进行整合。透过高密度1T巨集模组与某些提供刷新讯号的支持逻辑整合,可使存储器单元的动态特性透明化,设计者可在实施ASIC和SoC解决方案时,将存储器模组视为静态RAM。

1T SRAM是一种可授权IP,能从晶圆代工厂获得。但是,由于某些此类IP需要额外光罩层(除标准CMOS层外),增加了晶圆成本,因而限制晶圆代工厂的可选制造空间。为了使额外的晶圆加工成本物有所值,晶片上采用的总DRAM阵列大小,通常必须大于50%的晶片空间。大部份可用

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)

- 高压电池组监视器可实现先进的电池系统(10-14)

- 如何最大化延长即使具有老化电池的汽车电池组运行时间(08-14)

- 高准确度 60V 电量计如何测量电量?(09-12)

- Cypress电容式触控元件出货量突破10亿颗(08-14)

- 瑞萨电子3大ADAS检测系统解决方案简述(02-08)