用AndesCore N1033A-S处理器实现μC/OS-II的移植

μC/OS-II是一种代码公开、可裁剪的嵌入式实时多任务操作系统。该内核通过实现抢占式任务调度算法和多任务间通信等功能,使之具有执行效率高、实时性能优良等特点。另外,其占用空间非常小(最小可裁剪至2KB)并且具有高度可移植性,因此被广泛的应用于微处理器和微控制器上。

晶心科技 (Andes)作为亚洲首家原创性32位微处理器IP与系统芯片平台设计公司,推出的AndesCore™ N10系列产品N1033A-S, 搭配应用广泛的嵌入式实时操作系统μC/OS-II以及相关的软硬件开发资源,有效的帮助客户降低现有成本、提升系统效能、减少系统功耗,并缩短产品开发上市时程。本文将介绍如何将μC/OS-II移植到AndesCore™ N1033A-S处理器上。

1. 开发环境及处理器介绍

1.1 软/硬件开发环境

本移植过程使用的软件环境是AndeSight? v1.4集成开发套件,它是晶心科技最新推出的针对各种AndesCore?的软件集成开发环境,包括编译器、调试器、分析器以及强大的ESL工具。硬件平台采用晶心科技的FPGA评估板ADP-XC5,该评估板采用AndesCore? N1033A-S作为处理器内核,并具有丰富的片上资源。

AndesCore™ N1033A-S介绍

AndesCore™ N10系列产品N1033A-S是一款哈弗结构的32位RISC处理器内核,具有5级流水线(pipeline)及动态分支预测(Dynamic branch prediction)架构。N1033A-S新加入了最新AndeStar™ V2 指令集,把CPU效能推至1.66DMIPS/Mhz之上。同时还实现完整的Audio指令集,达到完全整合CPU与DSP功能的目标。N1033A-S还支持向量中断模式以及2D 直接内存访问(DMA)功能,更为实时信号处理添增效能。

2. μC/OS-II在N1033A-S上的可移植性分析

μC/OS-II具有高度可移植性,目前已经移植到近40多种处理器体系上,涵盖从8位到64位的各种CPU(包括DSP)。

μC/OS-II的正常运行需要处理器平台满足以下要求: 1)处理器的C编译器能产生可重入代码;2)用C语言就可以打开和关闭中断;3)处理器支持中断,并且能产生定时中断;4)处理器支持能够容纳一定量数据的硬件堆栈;5)处理器有将堆栈指针和其它CPU寄存器读出和存储到堆栈或内存中的指令。

AndesCore? N1033A-S内部提供了32个通用寄存器,其中R31被用来做专门的堆栈指针。32根地址线最多可访问4GB存储单元,因此只要系统RAM空间允许,堆栈空间理论不会产生限制。N1033A-S处理器提供的AndeStar? V2指令集包含了丰富且十分高效的对堆栈进行操作的指令。例如指令SMW(store multiple word)可实现仅使用一条指令将多个寄存器的值存储到堆栈中并同时更新堆栈指针位置,而且还能很好的处理地址非对齐字的存取。N1033A-S支持中断并能产生定时器中断,处理器中的PSW(Processor Status Word)寄存器中包含一个全局中断禁止位GIE,控制它便可实现打开和关闭中断。此外,AndeSight?集成开发环境中内置的编译器可以产生可重入代码,并且支持内联汇编,C环境中可以任意进行开关中断的操作。综上所述,μC/OS-II完全可以移植到N1033A-S上运行。

3. 移植步骤

为了方便移植,大部分的μC/OS-II代码是用C语言写的,用户只需要用C语言和汇编语言写一些与处理器相关的代码就可以实现移植。这部分工作的内容包括:一个完成基本设置的头文件os_cpu.h、一个与处理器相关的汇编文件os_cpu_a.S 和一个与操作系统相关的C代码文件os_cpu_c.c.

3.1在os_cpu.h中完成基本的配置和定义

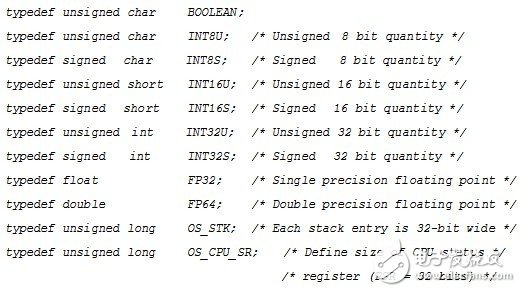

3.1.1. 定义与处理器相关的数据类型

为保证可移植性,μC/OS-II没有直接使用C语言中的short、int和long等数据类型的定义,因为不同的处理器有不同的字长。对于N1033A-S这样的32位处理器,其数据类型定义实现如下:

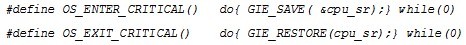

3.1.2. 定义中断禁止/允许宏

做为实时内核,μC/OS-II需要先禁止中断再访问代码临界区,并且在访问完毕后重新允许中断。 μC/OS-II定义了两个宏来禁止和允许中断:OS_ENTER_CRITICAL()和OS_EXIT_CRITICAL()。在N1033A-S处理器上的实现代码如下

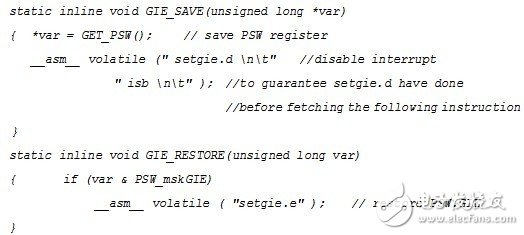

GIE_SAVE 和GIE_RESTORE的实现如下:

中断禁止时间是判断系统实时性的重要指标之一。中断禁止时间能否达到最短,不仅与操作系统的设计有关,还依赖于处理器结构和编译器产生的代码质量。从上面的实现代码看到,由于Andes处理器提供了setgie.d和setgie.e两条直接控制中断的开关的指令,整个禁止/允许中断的过程经过编译器产生的机器码只有3/2条,最大限度地减小了中断禁止时间。

3.1.3. 定义栈增长方向

μC

AndesCore uC OS-II 移植 操作系统 处理器 相关文章:

- 如何应用AndesCoreTM EDM安全访问机制(02-02)

- 浅析Buck变换器的电流取样电阻放置位置(12-31)

- 单相双Buck光伏逆变器的设计方案(02-18)

- uCOS-II在车载GPS移动终端中的应用(04-13)

- 实现统一通信的可移动性方法研究(09-19)

- 盘点STM32-NUCLEO开发与仿真平台(03-28)