带你了解TI的DSP入门芯片TMS320F28335

RL.bit.ENPIE = 1; // Enable the PIE block使能PIE

PieCtrlRegs.PIEIER1.bit.INTx5= 1; //使能第一组中的中断5

IER |= M_INT1; // Enable CPU 第一组中断

EINT; // Enable Global interrupt INTM

ERTM; // Enable Global realtime interrupt DBGM

也就是说,12组中的每个中断都要完成上面的相同配置,剩下的才是去配置自己的中断。如我们提到的EXINT,即外面来个低电平我们就进入

中断,完成我们的程序。在这里要介绍一下,DSP的GPIO口都可以配置为外部中断口,其配置方法如下:

GpioCtrlRegs.GPBMUX2.bit.GPIO54 = 0; //选择他们是GPIO口

GpioCtrlRegs.GPBMUX2.bit.GPIO55 = 0;

GpioCtrlRegs.GPBMUX2.bit.GPIO56 = 0;

GpioCtrlRegs.GPBMUX2.bit.GPIO57 = 0;

GpioCtrlRegs.GPBDIR.bit.GPIO54 = 0;//选择他们都是输入口

GpioCtrlRegs.GPBDIR.bit.GPIO55 = 0;

GpioCtrlRegs.GPBDIR.bit.GPIO56 = 0;

GpioCtrlRegs.GPBDIR.bit.GPIO57 = 0;

GpioCtrlRegs.GPBQSEL2.bit.GPIO54= 0;//GPIO时钟和系统时钟一样且支持GPIO

GpioCtrlRegs.GPBQSEL2.bit.GPIO55= 0;

GpioCtrlRegs.GPBQSEL2.bit.GPIO56= 0;

GpioCtrlRegs.GPBQSEL2.bit.GPIO57= 0;

GpioIntRegs.GPIOXINT3SEL.bit.GPIOSEL = 54;//中断3选择GPIO

GpioIntRegs.GPIOXINT4SEL.bit.GPIOSEL = 55;

GpioIntRegs.GPIOXINT5SEL.bit.GPIOSEL = 56;

GpioIntRegs.GPIOXINT6SEL.bit.GPIOSEL = 57;

XIntruptRegs.XINT3CR.bit.POLARITY= 0;//触发模式为下降沿触发

XIntruptRegs.XINT4CR.bit.POLARITY= 0;

XIntruptRegs.XINT5CR.bit.POLARITY= 0;

XIntruptRegs.XINT6CR.bit.POLARITY= 0;

XIntruptRegs.XINT3CR.bit.ENABLE = 1;//使能中断

XIntruptRegs.XINT4CR.bit.ENABLE = 1;

XIntruptRegs.XINT5CR.bit.ENABLE = 1;

XIntruptRegs.XINT6CR.bit.ENABLE = 1;

注意一点就是外部中断1和2只能对GPIO0—GPIO31配置;外部中断3和4、5、6、7只对GPIO32—GPIO63配置。

基于TMS320F28335信号处理板的设计与实现

硬件系统设计

1.1 方案概述

该系统主要功能是DSC通过ADC采样芯片对12路模拟信号进行同时采样。在DSC中进行数据处理后通过异步串行收发器上传到上位机。同时,上位机也可以通过异步收发器向DSC发送预先制定的命令,来控制信号处理板的工作模式和状态。

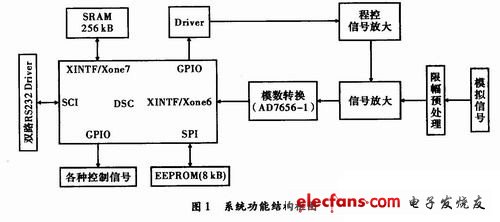

按照功能要求,整个硬件电路可分为3部分:电源模块、数字部分和模拟部分。其功能结构框图如图1所示。

1.2 电源模块设计

整个处理板的外部输入电压为5 V和±12 V,分别通过对应的电压转换芯片为模拟和数字部分提供不同的电压幅值。对于数字部分,电源模块需要为DSC提供1.9 V的核电压,同时为DSC的外围和其他芯片提供3.3 V的外围电压。本系统选用LT1963AES8集成芯片提供1.9 V,LT1963AEST-3.3集成芯片提供3.3 V。对于模拟部分,系统要求输入ADC的信号幅值范围在±12V内,所以系统分别选用LT1086IT-12和LT11 75IT把输入的±15V电压转换成±12V。

1.3 数字电路设计

数字部分电路主要是以DSC为中心的应用电路。该部分主要是对ADC传送的数据进行处理、存储,同时完成DSC同上位机的通信和数据传输。由图1可以看到,它包含以下几个部分。外围SRAM扩展,EEPROM扩展电路,SCI上位机通信接口电路。

1.3.1 外围SRAM扩展

考虑到TMS320F28335片内的RAM资源有限,加上程序空间和数据空间RAM仅为34 kB,16位数据宽度,从而需要对片内的RAM进行扩展,来满足较大量程序的运行。本系统选用Cypress公司的CY7C1011CV33-12ZSXE集成芯片,利用TMS320F28335提供的XINTF接口完成片外RAM的扩展。

XINTF是TMS320F28335所提供的一个非复用异步总线,用来完成外部异步器件的扩展。XINTF可以映射外设到3个固定的内存映射区域,当外部资源挂接到某个区域时,则需要通过XINTF的一个片选信号来进行外部资源的选定。

CY7C1011CV33-12ZSXE是一个CMOS的静态RAM存储器,其容量大小为64 kB,16位数据宽度。图2是外围SRAM扩展电路连接图。

如图2所示,本系统选用ZONE7区域作为RAM的外围扩展。DSC通过其XZCS7管脚向片外SRAM发送片选信号。WE信号用来控制DSC对片外SRAM的读写,当DSC的XWEo管脚为低电平,则DSC对片外RAM进行读写操作;XWEo为高电平,同时DSC的XRD管脚为低电平,则为读操作。

1.3.2 EEPROM扩展

考虑到系统在加电后,需要对一些设备的状态进行一些初始

DSP TI公司 TMS320F28335 相关文章:

- 基于AD73360和TMS320F2812的数据采集系统设计(12-06)

- 基于紫外检测法的智能型特高压验电器系统(03-17)

- 单一DSP控制两套三相逆变器的实现(08-31)

- 基于DSP生成SVPWM在逆变电源中的应用(11-09)

- DSP的大功率开关电源的设计方案(12-01)

- DSP处理器电源方案设计(02-08)