基于DSP和CPLD的低功耗多路数据处理系统设计

。为了防止数据丢失,在读数据的时候,RC[5:0]应该始终保持为高,因为如果CS[5:0]和RC[5:0]信号中同一位均保持为低超过40ns,就会启动一次新的采样,这样会造成没有被读的ADS7805产生一次新的采样而丢掉之前转换的数据,对整个系统的结果造成很大的影响。读完第6个ADC以后,在ARE的上升沿将FLAG标志拉高,这时计数器开始记数,根据记数器的数值,当2《cnt[2:0]《6的时候,将RC[5:0]和CS[5:0]同时拉低,这样有3个时钟周期的长度大概有100ns,保证了同时为低的时间不小于40ns,启动新一轮的采样。第二个always模块主要实现对FLAG标志位的判断和设定。当A[4:2]=000时,说明DSP开始读A/D采样数据,这时FLAG=0。当A[4:2]=101时,说明6个ADS7805数据已经被读完,需要进行新的采样,这时FALG=1。第三个always模块主要实现计数器的设计。记数时钟频率为30MHz。当FLAG为高且cnt[2:0]《7时,开始记数。当FALG为低时,对计数器进行复位。

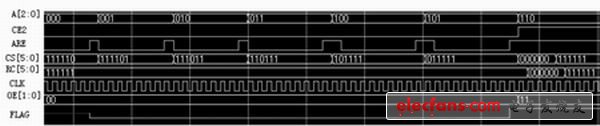

根据以上设计思路,成功地做到了对6路信号的采样和读取控制,达到了预期的效果。仿真波形如图2所示。

图2 CPLD仿真波形图

DSP软件设计

在进行DSP程序设计之前,先利用MATLAB的FDATOOL工具设计数字滤波器,将滤波器系数以.h文件形式导出MATLAB,在CCS中定义一个数组存放滤波器系数,就可以成功地将滤波器系数导入CCS。

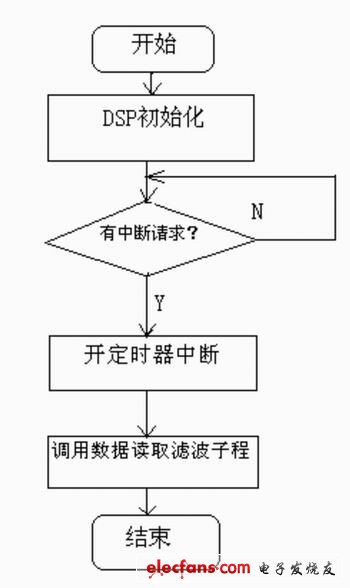

本文主要介绍DSP对多路信号读取并处理的软件设计方案。图3是整个程序的流程图。首先应该对DSP芯片进行初始化,主要包括对TMS320VC5502的PLL寄存器进行初始化、初始化系统中断向量表、EMIF的初始化和定时器的初始化。DSP通过EMIF接口对外围ADC的转换数据进行读取。整个数据读取和数字滤波工作是在定时器中断程序中进行的。定时器模块主要用来确定采样周期,即每来一个定时器中断就对信号进行一次采样并完成对信号的实时处理运算。因此,定时器的中断周期也就是采样周期,同时,也规定了DSP做一次信号处理运算所耗时间的上限,即必须在相邻两次的时钟中断之间完成一次处理所需要的运算和操作。然后初始化EMIF模块,这一部分比较重要,因为ADC转换好的数据是通过EMIF接口送进DSP芯片的。ADC芯片在本系统中被内存化了,也就是说,从DSP芯片的角度看,读写ADC芯片和读写异步SRAM没有差别,因此,要将ADC芯片也分配到片外存储空间里,本系统采用的方法是将ADC芯片分配到CE2空间0x400000~0x400005连续的6个地址,使用异步16位SRAM的配置方式来配置CE2空间的控制寄存器。当有中断请求时,DSP就进入频率为40KHz的定时器中断,进行读取和滤波工作。

图3 DSP程序流程图

系统功耗估计

通过查阅芯片手册可以知道,TMS320VC5502需要的1.26V核心电压供电能力为250mA,3.3V的I/O电压和锁相环I/O电压的供电能力为50mA, DSP芯片的功耗为480mW。ADS7805芯片的功耗典型值为100mW,6个共计600mW。CPLD的3.3V电源消耗电流的典型值为100mA,即330mW。这样,整个系统功耗大概为1.5W。在使用电池供电的情况下,这个功耗大小也是可以接受的。例如,使用一个12V输出、50Ah的蓄电池,理想情况下可以对系统供电400小时。即使考虑电压转换过程中的能量损耗,用上述规格的蓄电池对系统供电40个小时也是可行的。

结语

本文介绍了一种基于DSP和CPLD的低功耗多路数据采集系统。 CPLD简化了硬件设计,可以很方便地对系统进行在线编程,具有很高的灵活性。本系统已应用于军事等具有低功耗、高性能要求的领域。

- 基于AD73360和TMS320F2812的数据采集系统设计(12-06)

- 基于紫外检测法的智能型特高压验电器系统(03-17)

- 单一DSP控制两套三相逆变器的实现(08-31)

- 基于DSP生成SVPWM在逆变电源中的应用(11-09)

- DSP的大功率开关电源的设计方案(12-01)

- DSP处理器电源方案设计(02-08)