基于芯片测试的环路滤波器设计

2GHz(fPFD=25MHz,RSET=5.1k),根据测试要求进行综合的考虑,设定了环路带宽75kHz,相位裕度50°的约束条件。在进行ADF 4153的外围电路设计时,首先需要确认所使用的VCO型号及其标称性能。然后再根据ADI公司提供的ADIsim-PLL软件进行三阶环路滤波器的设计。从软件得出C1~C3、R2、R3的具体取值,再根据现有的标称电容电阻值进行调整,反算出实际设计的环路带宽及相位裕度。实际数据如表1所示。

由此,我们确定了环路滤波器中各个电容、电阻的取值,并设计了可用于ADF 4153芯片测试的电路原理图,如图4所示。VCO的输出不仅需要连接外部频谱仪进行测试,还需要通过电容反馈到ADF 4153的REFINA端,同时REFINA端还需要预留SMA头用于射频输入频率范围及灵敏度测试。一个简单的电阻网络用于完成VCO输出信号功率的再分配。

图4环路滤波器及射频电路设计

3 环路滤波器的测试验证

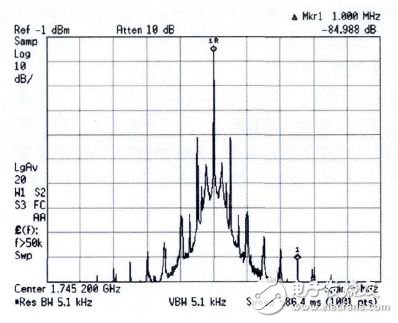

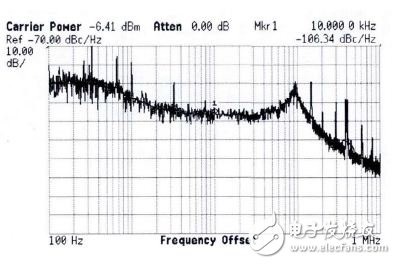

在仿真的基础上,我们设计并加工了ADF4153的测试板,并按照计算的电容、电阻值组成了环路滤波网络。采用Agilent8257D射频信号源提供250MHz作为fREFIN,通过SPI端口设定fPFD=25MHz,N=69,4/5分频模式,ICP=5mA,FRAC=101,MOD=125。使用频谱仪测量输出信号,能够正常锁定在1.7452GHz,如图5所示。图6为该频点的相位噪声测试图,实测相位噪声为-106.34dBc/Hz。环路带宽约为85kHz,与理论值77.3kHz存在一定的差距。这是由于在仿真时并没有考虑测试板走线及测试插座等存在的寄生电容所导致的偏差,但仍在合理范围以内。

图5输出信号频谱

图6相位噪声测试图

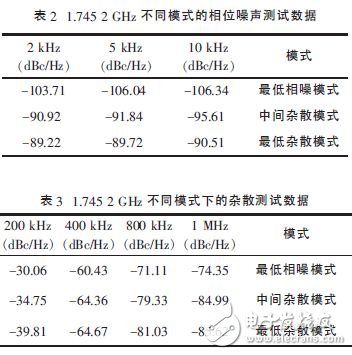

针对芯片进行不同工作模式下的相位噪声及杂散进行测试,测试结果如表2、3所示。

数据手册规定最低的相位噪声模式下5kHz频偏的相位噪声PN≤-95dBc/Hz,实测该点为-106.04dBc/Hz,测试结果满足要求。

数据手册规定中间杂散模式下1MHz频偏的杂散SN≤-65dBc/Hz,实测该点为-84.99dBc/Hz,测试结果满足要求。

综上所述,该滤波器的设计能达到预期的设计目标,满足不同模式下的杂散及相噪测试的要求,可用于ADF 4153芯片的性能测试。

4 结束语

本文主要基于芯片测试目的,针对外围电路中的环路滤波器设计来进行讨论,文中给出了一种简单、易行的工程化计算方法和流程,并对其进行了验证测试,测试结果满足芯片测试的需要。这种方法已经应用于多款小数分频频率合成器的测试电路的设计中。

ADF4153 环路滤波器 芯片测试 频率合成器 相关文章:

- 半导体厂商如何做芯片的出厂测试(05-18)

- 低相噪高纯谱数字捷变频合器的实现(02-11)

- LT3751如何使高压电容器充电变得简单(08-12)

- 三路输出LED驱动器可驱动共阳极LED串(08-17)

- 浪涌抑制器IC简化了危险环境中电子设备的本质安全势垒设计(08-19)

- 严酷的汽车环境要求高性能电源转换(08-17)