低相噪高纯谱数字捷变频合器的实现

摘要:介绍一种X波段频率合成器的设计方案,此方案将直接式和数字锁相相结合,完成快速捷变功能。

引言

现代雷达对频率合成器相位噪声、快速捷变能力、灵活多变的波形产生、带内杂散提出越来越高的要求。全相参直接式频率合成器具有较高的频率稳定度,短的跳频时间,直接式频率合成器的缺点是杂散抑制,而且设备量庞大。锁相频率合成器的缺点在于如果环路总分频比太大,会严重恶化输出的相位噪声;且频率变换速度较慢。所以将直接倍频与数字锁相结合,利用开关的快速切换速度、直接倍频的频率稳定性、数字锁相的灵活多变,完成方案的设计。

系统框图

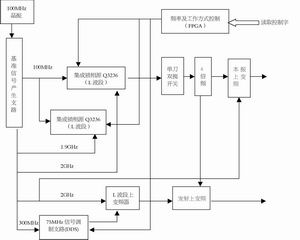

图1为X波段频率合成器原理框图。

当数字锁相环间歇工作(数字锁相环只用于频率捕获)时,数字锁相环锁定时间需要40~50ms。这是由于在数字锁相环停止工作期间环路滤波器输出电压总是处于饱和状态,当数字锁相环重新工作时必须经历一段较长的恢复时间才能正常工作。数字锁相环的频率捕获时间过长是它的缺点,但是它的数字接口灵活易变,一条环可完成多个稳定频率点的需求,相应的设备量少。电子开关的速度为nS级,可完成快速捷变的需求。在频率控制时稍加设计,就可将两者的优点有效的结合起来。当开关由第一条环选向第二条环时,第二条环已在上一个时钟稳定,捷变时间由开关决定;同时,第一条环由数字界面控制,改变频率。如此类推,下一个时钟时,当开关由第二条环选向第一条环时,第一条环已在上一个时钟稳定,捷变时间由开关决定。由此,很好的解决了直接倍频的难点—杂散抑制。

再由倍频器展宽频带。

X波段上变频器是杂散信号的主要来源,因其是宽带混频,通带内会出现交调分量,这里采取两项措施解决,一项措施是计算好混频器的输入信号(fi)和输入本振信号(fL),使mfL±nfi(fL+fi除外)尽可能少的落在带内。另一项措施是在混频器后使用开关滤波器组件,将宽带滤波器分成几个窄的滤波器,选择相应的滤波器,就可有效的抑制交调分量。

图1 频率合成器框图

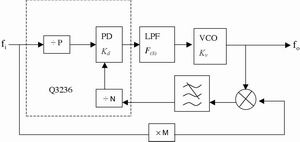

图2 数字锁相原理框图

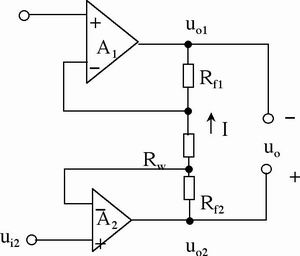

图3 同相并联差分放大器

设计要点

数字锁相频率合成器

对于工作频率高、变频间隔相对较小的锁相合成器,如果采用前置分频法,则环路分频比较大。在反馈支路进行频率下移,可有效减小环路分频比,有利于改善系统的相位噪声和动态相应特性,这是目前常用的一种锁相合成器。工作原理是参考信号与反馈信号在PD中进行相位比较,输出电压通过环路滤波器LPF抑制噪声和高频分量来控制VCO,系统通过控制反馈支路移频后的分频比,实现捷变频,环路锁定时,输出频率为f0=(m+N/p)fi。其框图如图2所示。

环路增益的选择:在选择环路带宽时,环路带宽要远远小于环路增益,所以在设计时,在鉴频/鉴相器和环路滤波器之间增加一级放大器,则大大提高了环路增益,可确保相位噪声指标的提高。放大器电路如图3所示。

因为同相并联差分放大电路结构对称,应选用参数对称的外电路,即Rf1=Rf2=Rf,此时,差模增益为:

由上式可得出,同相并联差分放大器,仅改变Rw大小就可以很方便的调节增益,对外电路不需要匹配电阻,输出可获得极高的共模抑制比。

环路带宽的选择:压控振荡器相位噪声的功率主要集中在低频部分,锁相环路的误差传递函数的频率响应的高通过滤作用是相当显著的, 在F<fn的低频端,衰减量以每10倍频程20dB上升。由以上分析,仅从过滤压控振荡器噪声来说,应选择fn越大越好。

但是作为参考振荡器的晶振噪声作用到环路鉴相器的输入端,环路对晶振噪声呈低通过滤,过滤作用取决于闭环传递函数的频率响应;在F<fn的高频段内,以每10倍频程-10dB下降。由以上分析,仅从过滤输入晶振相位噪声而言,环路的fn越小越好。

在同一坐标系中,先作出VCO的相位噪声谱,再作出经N2倍增后的晶振相位噪声谱,可以找到两条谱线的交点,只要把环路的fn选择在这个交点频率上,输出相位噪声功率就是最小。只要将所有的噪声按高通型和低通型两类归并,再用前面的方法同样可以完成最佳fn的设计。

环路滤波器采用有源比例积分滤波器,其特性接近理想积分滤波器,有两个独立可调参数,并具有滞后-导前特性,有利于环路的稳定。

基于DDS的线性调频信号源

DDS主要由相位累加器、sin幅度变换器、D/A转换器和低通滤波器(LPF)等组成,其核心部件是相位累加器,如图4所示,在系统时钟的作用下,由相位累加

- 基于芯片测试的环路滤波器设计(02-27)

- LT3751如何使高压电容器充电变得简单(08-12)

- 三路输出LED驱动器可驱动共阳极LED串(08-17)

- 浪涌抑制器IC简化了危险环境中电子设备的本质安全势垒设计(08-19)

- 严酷的汽车环境要求高性能电源转换(08-17)

- 适用于工业能源采集的技术 (08-10)