低相噪高纯谱数字捷变频合器的实现

时间:02-11

来源:不详

点击:

器完成频率累加,并将每次累加结果作为取样地址,周期性地扫描正弦波的波形存储器,并通过D/A转换器把结果变换成电压波形。

输出频率、频率控制字、系统时钟频率三者的关系为:

式中:FO—输出波形的频率;K—频率控制字;

FCLK—系统时钟频率;N—相位累加器位长。

DDS合成的信号除主谱外,存在大量的杂散分量,这些杂散分量主要有三个来源,一是相位截断误差引起的,这可用相位累加器输出相位截短后用于寻址相/幅变换表的位数来衡量,二是波形存储器ROM的数据位数是有限的,引起波形幅度量化误差,这由相/幅变换后输出数字的位数和DAC位数决定,三是由于DAC的非理想特性,阶梯波在DAC输出端产生谐波与杂散分量。在本系统中DDS芯片使用ADI公司的AD9854作为其核心,相位截短引起的杂散可忽略不计,量化误差可根据实际的波形带宽,采用过采样技术加上滤波获得更高信噪比。DAC的非理想特性,在实际使用中只能选择具有良好线性度的DAC来改善DDS输出信号质量。

实验结果

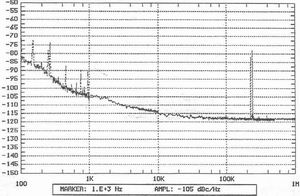

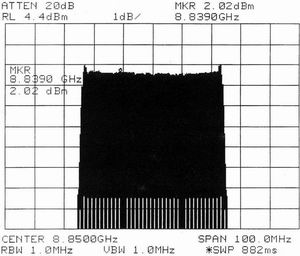

按照图1所示框图完成的X波段频率合成器本振路单边带相位噪声功率谱密度曲线(fo=9500MHz)如图5所示,发射路带宽为50MHz线性调频信号波形如图6所示。

图4 DDS功能方框图

图5 单边带相位噪声功率谱密度曲线

图6 50MHz线性调频信号波形

结语

数字集成锁相环因其易于调试、体积小、功耗小已成为间接频率合成器的核心,DDS因其相对带宽很宽、可编程及全数字化结构等优越性得到广泛应用,通过分析和系统中验证,本方案得到比较满意的效果。

- 基于芯片测试的环路滤波器设计(02-27)

- LT3751如何使高压电容器充电变得简单(08-12)

- 三路输出LED驱动器可驱动共阳极LED串(08-17)

- 浪涌抑制器IC简化了危险环境中电子设备的本质安全势垒设计(08-19)

- 严酷的汽车环境要求高性能电源转换(08-17)

- 适用于工业能源采集的技术 (08-10)