Intel第六代处理器 Skylake CPU、GPU、主板完全解析

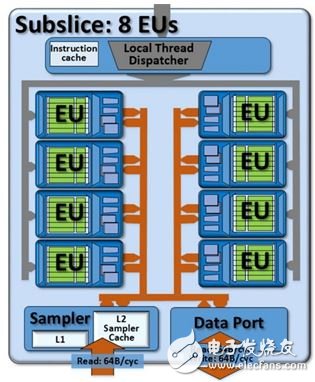

增加?从架构图中我们可以看到,每组 Subslice 内只有 8 个 EU,也就是说每个 Thread Dispatch(线程调度器)、Sampler(采样器) 可以更有效率分配。而运算效能的部分,可以藉由堆栈更多的 Subslice 来达成(也就是更多的 EU),让 Broadwell 运算效能更高。因而在 Broadwell 上,看到的 EU 数量大多是 24 或 48 等等 8 的倍数。

▲Gen 8 与 Gen 9 皆采用 8 个 EU 的配置,并且由增加 Subslice 的总数,来达到提升整体效能的目的。简单来说,就是靠一堆运算单位来堆出效能。

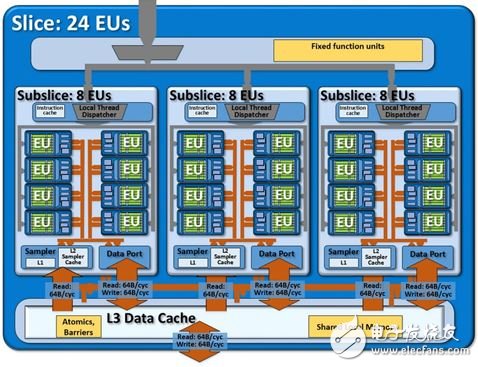

到了 Skylake 时期,绘图核心架构被称为 Gen 8.5 或 Gen 9,从已知的架构来看,设计与 Broadwell 的 Gen 8 相同,差别仅在于显示核心内 Slice 数量最多增加到 3 组,EU 从原本的 24、48 个,增加到最多 72 个。

▲Skylake 时期 Slice 内有 3 组 Subslice,每个绘图核心内又有 3 组 Slice,因此EU总计有 8x3x3=72 个。

GPU 特色 2:型号新命名原则

刚刚说过,EU 从原本的 24 增加到最多 72 个,因此绘图核心的型号增加最高的 GT4 等级,再往下依序是 GT3、GT2、GT1。当然这是给厂商以及内部使用的型号,对消费者 Intel 仍保留了 Iris Pro、Iris、HD Graphics 等品牌营销代号。

且为了精简型号代码,型号从原本的 4 码变更为3码,像是 Iris 540、HD Graphics 515 等型号。你可以从型号中得知绘图效能高低,Iris Pro 优于 Iris 优于 HD Graphics。内建 72 个 EU 最高级的 GT4e 就是 Iris Pro,48 个 EU 的 GT3 与 GT3e 就是 Iris,再往下就是 HD Graphics。

重生的 GPU 效能

过往 Intel 的绘图效能都只有被嘲笑的份,但从 HD Graphics 时代开始已经有明显的进步,到了近几年,Iris 系列更是能与中低阶独立显示适配器抗衡。内建就能有不错的效能,何必多花钱买独立显卡。但仍有许多消费者认为独立显示芯片还是比较好,这造成了部分笔电上,搭配的独立显示芯片,竟然比内建的 Intel 显示效能还要差的怪现象。目前最高级的 Iris Pro,也就是 GT4e 等级,约莫等同 GTX 740、HD 7750。

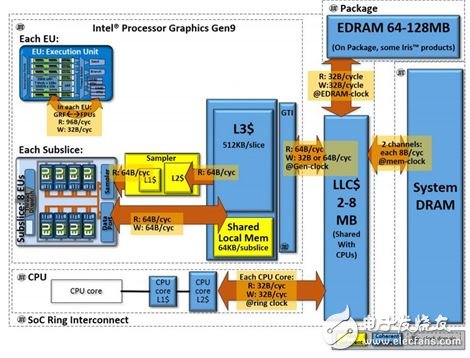

▲Skylake 基本的 Gen 9 架构配置如上,可视情况再增加 Slice 以提升效能。

GPU 特色 3:eDRAM 运作改变

eDRAM 是 Haswell 开始搭载的硬件设计,简单来说它的作用为 L4 Cache。会增加这功能,主要是因为 IGP(整合型绘图芯片) 经常面临内存带宽不足的问题,Intel 提供的解决方式就是在处理器内,有个独立的内存区块也就是 eDRAM,频率最高 1.6GHz。

之所以位于独立区块,原因是这区块工艺不同于其他区域,且独立的好处是能随市场增加或减少内存容量,操作弹性较高。有意思的是,这 eDRAM 并非完全隶属于 GPU,而是可随状况动态调整支持 CPU(处理核心) 或 GPU(绘图核心)。这意味着,当安装独显的时候,eDRAM 就会完全替 CPU 工作,因为此时 GPU 是关闭的。

在Skylake时期,绘图核心可与处理核心共享 LLC(L3快取),但跟 Haswell 时期相比,差异在于 eDRAM 运作方式改变。现在 eDRAM 控制器位于 System Agent,此时 LLC 能空出 512KB 的空间,让 eDRAM 被视为 LLC 与系统主存储器之间的快取机制。

然而,并非所有 Skylake 处理器都有 eDRAM 设计,像是 Core i7-6700K 就没有 eDRAM。一般而言 eDRAM 容量约 64 至 128MB 不等,最高频率 1.6GHz,读写的总线采分离设计,各有 32byte 的传输量。

▲eDRAM 可动态服务 CPU 或 GPU,但并非所有产品都有配制 eDARM。

GPU 特色 4:设计小改效率提升

虽说 Gen 9 跟 Gen 8 的架构设计大同小异,但深层仍有些变动,在此一并解说差异。基本的运算单位 EU,现在可将当下执行的线程中断,改执行其他线程,也就是 EU 可支持多任务的运作。此外,支持列表还有 round-robin,以及执行途中不中断的 32bit 浮点数原子式操作。

先前说过 LLC 空出多余的空间,这让 Shared Virtual Memory 的写入效能提升。材质样本现在可支持 NV12 YUV 格式。

此外,单一 Slice 内 L3 Cache 容量从先前的 384 至 576KB,增加到 768KB。并有共享内存,用以存放各 EU 间互通的数据。Skylake 的绘图核心靠的是 Graphics Technology Interface 与其他硬件沟通,它位于架构图最底下的位置,即为绘图核心的沟通接口,意义上与 LLC 连接。

Gen 9 架构的规格、效能,大多与 Gen 8 相同,但靠着比较多的 EU 总数,效能面还是可以胜过自家前代产品。且靠着已经成熟的 Slice 架构配置,可增减需要的 Subslice 数量,藉此作出产品区隔与效能差异。

▲中央橘

Skylake 主板 intel GPU CPU 相关文章:

- 电脑面板插头与主板插座巧配对(03-01)

- 意法半导体:计算机主板和笔记本主板方案(02-03)

- 英特尔新一代超低功耗超小尺寸Atom曝光(06-18)

- PC的主板是如何给CPU和GPU供电的?(02-10)

- 【科普】PC主要硬件CPU、主板、显卡的电源需求(02-24)

- IGBT 驱动器提供可靠保护(04-14)