Intel第六代处理器 Skylake CPU、GPU、主板完全解析

电相数 4 相就能用,中高阶版本也不过 8 至 12 相。过往 24 甚至 36 相的供电已经不存在,但取消 FIVR 后会不会再度复苏值得观察。

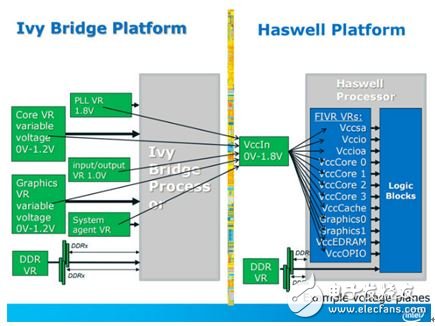

▲FIVR 是 Haswell 平台开始使用,图中可看出它整合了原先 Ivy Bridge 主板的大量供电模块。供电单一化之后,有助于提升供电效率,但也因为 FIVR 内建于处理器内,因此造成处理器的 TDP 因而提升。

FIVR 的隐忧与缺陷

然而 FIVR 会被取消肯定有其弊病,部分认为 FIVR 增加了处理器设计的复杂程度,毕竟必须将 FIVR 整合于处理器内。其次,主流的处理器 TDP(Thermal Design Power),从 Ivy Bridge 时期的 77W 提升到 84W,据称也是 FIVR 的影响。

此外,先前在 IDF 2015 大会上,有提到 FIVR 在 TDP 仅 4.5W 的 Skylake-Y 中表现不佳,因此可能是 Intel 决定整个架构删除 FIVR 的主因。

特色 4:BCLK 独立,超频更容易

先前 3 项特点对于部分玩家来说可能无感,但 Skylake 让 BCLK 独立,不会像过往与 PCI-E 频率连动,造成超频的瓶颈。虽然处理器倍频依然被锁,但 BCLK 可从 100MHz 超到 133MHz,相较于过去只有 5 至 10% 的超频幅度形成强烈对比。

Skylake 设计革新不仅于此

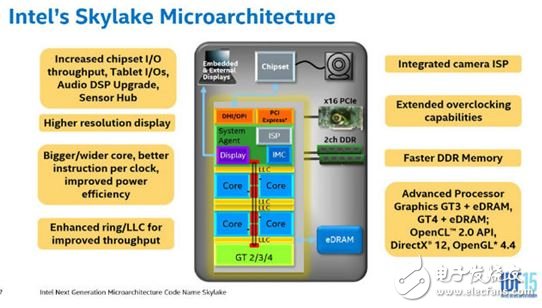

Skylake 除了上述比较容易理解的 4 项特点外,在 GPU、架构方面还有很多新的设计,举凡 EU 数量增加、供电设计更有效率、强化分支预测器等,都是 Skylake 的设计革新。但碍于篇幅有限,CPU 篇到此做个段落。

整体而言,Skylake 对我们而言不仅有架构上的改变,也有工艺上的提升,对于消费者来说,DDR3 与 DDR4 并存提供了更多的选择空间。对于玩家而言,BCLK 独立强化超频性,也是值得期待的特色。但新设计可能会带来额外的副作用,就如同当年的 FIVR 一般,新的设计会不会有其他问题,过阵子应该就会知道。但目前而言,Skylake 还是值得期待的新产品。

▲Skylake 的特色不仅只有上述 4 点,在 GPU、PCH 甚至是功能方面都有新功能或改进。个人认为,虽然近年处理器规格与效能进步幅度如挤牙膏般,但 Skylake 算是值得试试的产品。毕竟前面的 Haswell Refresh 与 Broadwell 太令人失望了,你说是不是?

GPU 篇

前文提到了Intel新处理器 Skylake 的 4 大特点,包括工艺提升、支持 DDR3 与 DDR4、取消 FIVR、BCLK 独立等功能。当然这仅止于处理器层面的变化,Skylake 平台还有绘图核心的改变,以及主板芯片组的改进。这次让我们来看看,Skylake 在绘图核心有哪些改变。

Intel 这几年处理器的效能增长如挤牙膏般一滴滴被压榨出来,而且绝大多数的增长都是显示核心层面,而非处理器本身的运算效能提升。从 HD Graphics 时代开始,Intel 显示核心的地位逐渐提升,近几年甚至能达到中低阶 NVIDIA 与 AMD 独立显卡的效能表现。

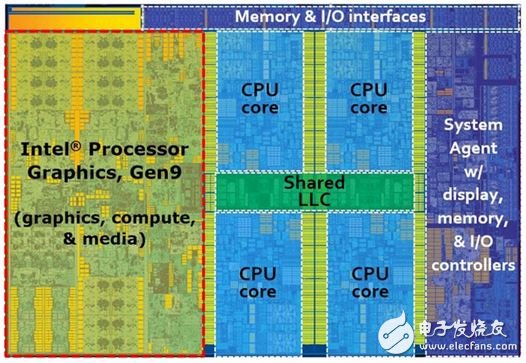

试想,当每颗处理器都有内建不亚于低阶独立显卡的显示效能,何必选择独立显卡呢?一方面可减少耗电量,再者也能释放计算机的可用空间。这次 Skylake 绘图核心主要在架构规模上提升,并且给了它个新的命名原则。

▲Skylake 的处理器分配如上图,最左侧即为绘图核心。

GPU 特色 1:EU 规模暴增

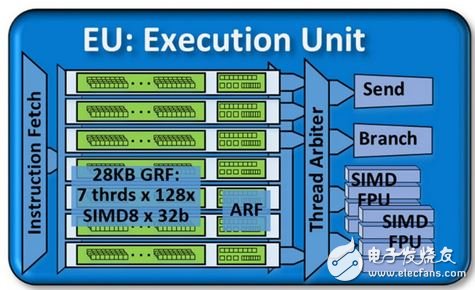

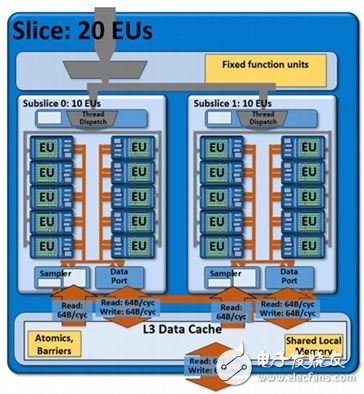

EU 是什么?EU(Eexecution Uunit) 是 Intel 绘图核心基本的运算单位,地位等同于 NVIDIA 的 CUDA Core,以及 AMD 的 ALU(Arithmetic Logic Unit)。过去在 Haswell 上使用的架构为 Gen 7.5,是将 10 个 EU、Thread Dispatch(线程调度器)、Sampler(采样器) 等组件,共同组成 1 组 Subslice。

若将 2 组 Subslice、Fixed function units,加上 L3 Data Cache,就成了完整的运算单元 Slice。因此 Slice 内有 20 个 EU,这也是为什么在 Haswell 上,完整的绘图核心规格都是 20 或 40 个 EU,例如 Core i7-4770K 的 GT2 有 20 个 EU,Core i7-4770R 的 GT3e 是 40 个 EU。至于低阶产品,核心架构肯定是会删减,因此只有 1 组 Subslice 构成 Slice,像是低阶的绘图核心 GT1 就只有 10 个 EU。

▲EU 是基本的运算单位,即便如此,内部还是有许多次层级的组件。

Gen 9 架构换汤不换药

Broadwell 时代进化到了 Gen 8 架构,此时 Slice 内的架构设计略有变化,每组 Subslice 内仅存 8 个 EU。你可能会问,这样效能不就更差了吗?的确,若 Slice 内仅有 2 组 Subslice 的话确实会让效能降低,但 Intel 让 Slice 内增为 3 组 Subslice,让整体的运作效率提升。

▲Gen 7.5 架构内 Subslice 有 10 个 EU,后来到了 Gen 8 时期为了效率,删减为8 个 EU。

为何 Broadwell 重新排列组合后效率会

Skylake 主板 intel GPU CPU 相关文章:

- 电脑面板插头与主板插座巧配对(03-01)

- 意法半导体:计算机主板和笔记本主板方案(02-03)

- 英特尔新一代超低功耗超小尺寸Atom曝光(06-18)

- PC的主板是如何给CPU和GPU供电的?(02-10)

- 【科普】PC主要硬件CPU、主板、显卡的电源需求(02-24)

- IGBT 驱动器提供可靠保护(04-14)