如何在FPGA内实现最佳化车用MCU设计方案?

在汽车电子中广为采用的微控制器(MCU)正快速面临时间和成本的压力。使用MCU的主要优势一直以来都是‘创造具有高性价比的高阶系统整合’。然而,在此一优势之下,有一些与元件本身相关的潜在成本是超乎于其单价水平的。例如,若选用的元件无法创造所需特性,则必须增加外部逻辑、软件或其它整合元件。

再者,目前汽车终端市场对于需求的变化屡见不鲜,以至MCU很快就变得不适用;许多具有专门特性以及固定专用界面数量的MCU,经过短暂的评估后即无法满足市场需求。因此,系统供应商不得不重新设计硬件及编写相关软件,在某些情况下,甚至必须更换处理器核心。

MCU的困境

MCU制造商正被迫面对会为整个市场带来巨大影响的挑战。MCU是针对应用而设计的元件;因此必须针对个别应用,设计具有不同性能组合的新元件。要以一个单一核心架构来满足这个广大市场,制造商必须提供多款MCU系列,提供不同的界面与功能。而市场上大部分的实例显示,目前的特性组合无法具体满足客户的需求,为了能够量产,必须在一个特定核心架构上改变新界面与功能。

过去的MCU是以旧有技术搭配相对低的制造成本来实现,在过去这是个成功的方法。但现在,为实现更高阶的系统整合,厂商不断采用先进制程技术,开发新的变种MCU所需费用变得相当可观。由于只有少数客户会下订单,因此,为满足单一客户需求而生产如此特殊的元件便不再具有商业意义。

因此,新的变种MCU被设计成具备越来越丰富的特性,以吸引整体市场,它正向标准产品发展,不再是针对特殊应用的元件。然而虽然这些标准产品的功能非常强大,但其成本也相对大幅增加,最后变得更难满足诸如汽车电子等对成本非常敏感的市场。

除了改变引起问题的根源——芯片上的固定功能,我们别无他法。很明显的,我们需要一种新的设计方法。

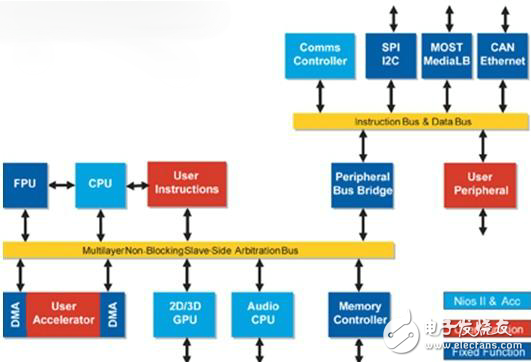

图1:此汽车资讯娱乐平台具有多个子系统、可扩展界面以及功能。

灵活的MCU概念

打破这个僵局的方法,是使用FPGA在芯片上实现灵活的功能。FPGA能显着缩短工程开发时间以及降低多次芯片返工成本,为MCU提供一个强而有力的可行替代方案。例如,采用基于FPGA的方法为汽车音响和导航设备开发一个灵活的绘图系统,可将开发时间缩短6个月。

与不具备所需特性的MCU不同的是,在设计过程中,可根据需要对FPGA进行编程和改编,以加快原型产生速度及产品上市时间。若需求改变,还可在现场对FPGA进行升级——即使元件已被安装在产品内。

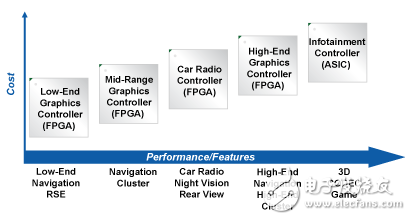

相较于传统控制器,FPGA已成为汽车绘图控制器所采用的主要设计方法。虽然为了诸如绘图等独立功能所设计的低价FPGA能广泛地为汽车市场所接受,但为实现可编程能力,仍需在芯片上做出巨额投资,因此扩增的复杂功能也将使得可编程元件价格趋于昂贵。

但随着目前已能从FPGA无缝转换为结构化ASIC,一个灵活的微控制器已兼具了价格竞争力,它从一个预定义的大型元件库与可扩展建构模组中所选取的性能也可以具体满足客户需求。

它与传统MCU的主要区别在于,从原型FPGA到最终MCU的无缝转换过程。CPU和汇流排架构对灵活的MCU概念来说都是特殊的,且对于特定客户应用,它们可将所需特定功能及特性映射到设计中。

图2:FPGA到ASIC整合提升了控制器的性能和特性。

RISC CPU

在Altera设计概念中使用的CPU是软RISC处理器。然而,与一般情况不同,该处理器并不是建构在一个预先设定好、无法改变的芯片内。相反地,它采用的作法是依据系统架构师/设计工程师,借助可用工具定义的规格自动产生,并与整个电路所需的其余逻辑同时载入FPGA。因此对于特定应用需求,可使用相关开发工具对处理器核心进行参数化。更重要的是,它可根据所需功能以及实现这些所需功能所需的逻辑资源,无缝地实现设计。

在基于Altera的灵活MCU应用中,Nios II嵌入式处理器采用一款带32位元独立位址和资料汇流排的标准RISC架构。两个汇流排都透过独立快取记忆体执行,且可独立地连续馈送到汇流排系统。最后,系统架构师决定对程式码和资料采用个别记忆体或是两者共用记忆体。任何处理器包含的功能单元都呈现在Nios II嵌入式处理器中,根据不同设定决定它们的特性。例如可选择硬件乘法器、桶式移位器以及硬件除法器作为选项,同样地,对指令和资料缓冲记忆体进行精确的处理,其尺寸可不同或是彻底被排除在外。

汇流排架构

传统上在MCU内一直是采用单汇流排,一个仲裁器用于监控汇流排,以便使汇流排成为一种分散式资源。随着作为系统中心资源的汇流排迅

- 安森美半导体配合中国消费类医疗市场趋势的半导体方案应用案例研究(07-20)

- 人工智能实现的流派 FPGA vs. ASIC看好谁?(08-27)

- 基于Xilinx Spartan-6 FPGA加速纹理映射的实现(09-08)

- 基于VHDL和CPLD的智能数字电压表设计(10-09)

- 浅谈降低100G系统功耗的六大关键技术(02-26)

- 赛灵思应用解决方案:ASIC原型与仿真(02-14)