智能手机省电秘诀:看如何从设计源头来降低功耗

处理器的负荷在日益增加。美国谷歌公司2012年3月将"Android"应用的容量限制由50MB提高到了4GB 注1)。今后亮相的应用将处理更多的数据,执行更加复杂的处理工作。

注1) 虽然应用APK文件的容量限制依然为50MB,不过最多可以使用2个最大2GB的扩展文件。

"终端厂商要求‘在保持当前耗电量不变的情况下提高性能’"(半导体厂商)。为此,处理器需要实现能够轻松处理今后亮相的高级应用,并最大限度降低耗电量。

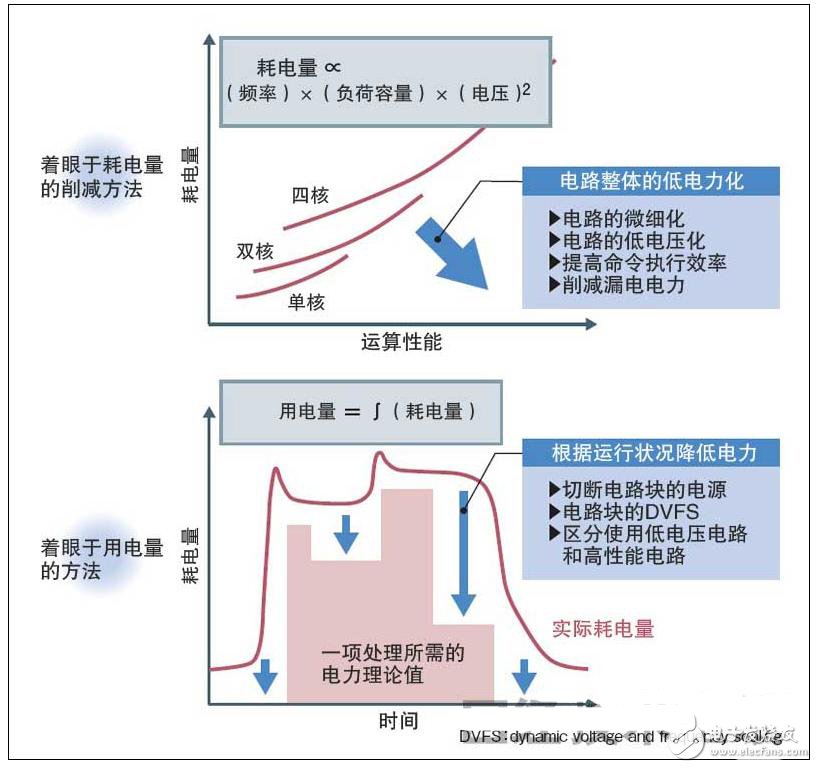

处理器的低耗电量化有两大方向(图6)。一是提高单位电力的处理性能(电力效率)。另一个是尽量减少通常处理时无需消耗的电量。

图6:在提高电路的电力效率以及进行极其细微的电力控制两方面努力

为降低应用处理器和基带处理LSI的耗电量,在两个方向采取举措。需要通过微细化和低电压化等提高电路的电力效率,根据运行情况彻底对电力进行极其细微的控制。

最大限度提高电力效率

为提高处理器的电力效率,各半导体厂商纷纷致力于半导体的微细化、电路的低电压化以及漏电的削减等。LSI的动态耗电量与工作频率、负荷容量以及电源电压的平方乘积成正比。尽量削减这些要素就能以更少的耗电量执行相同的处理任务。

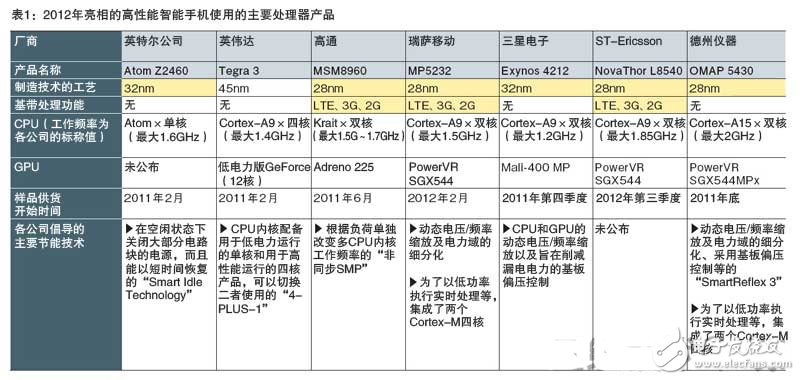

半导体的微细化在2012年是具有里程碑意义的一年。预计采用32nm/28nm工艺技术制造的产品将配备于智能手机(表1)。虽然漏电功率容易增加,但由于电路负荷容量减小,因此可以相应削减耗电量。数年后的22nm/20nm工艺的应用也有望利用这一效应。

技术壁垒较高的是低电压化。虽然半导体芯片截至90nm工艺一直在随着微细化顺利降低电压,但之后SRAM的误动作成为瓶颈,低电压化越来越难以实现。目前的便携终端用处理器的标准电压只降到1.0~1.1V左右,最小驱动电压降到0.8~0.9V左右。因此需要从根本上改进电路技术。

推进这类研究的是美国英特尔。该公司试制出了电力效率在阈值电压附近最高的x86处理器"Claremont"。这是通过开发能以0.28V的极低电源电压正常运行的电路群来实现的。以接近阈值电压的0.45V电源电压运行时,工作频率为60MHz,电力效率最大为5830MIPS/W(整体耗电量为10mW)。以1.2V运行时,工作频率最大为915MHz,电力效率为1240MIPS/W(整体耗电量为737mW)。

漏电功率对策也在推进

要想提高电力效率,还必须削减漏电功率。韩国三星电子在"Exynos"处理器上采用32nm工艺制造技术时,导入了high-k栅极绝缘膜/金属栅极(即HKMG)。

与32nm工艺中未导入HKMG时相比,栅极漏电流降至约1/100,整体漏电流降至约1/10。另外,三星电子还首次采用了基板偏压技术*。目的是根据裸片上的漏电功率和性能的监控信息,减小制造偏差造成的性能下降和漏电功率。

*基板偏压技术=在硅基板上加载偏压以动态控制阈值电压的技术。通过加载负电压提高阈值电压以暂时抑制漏电流的后基板偏压,或者通过加载正电压降低阈值电压以暂时提高速度的前基板偏压。

为尽量削减正常处理时无需消耗的电力,而实施的对策是根据负荷改变工作频率和电压的DVFS*,以及以电路块为单位的电源切断和时钟切断操作。处理器本来就导入了以动态控制电力为目的的技术。通过将这些技术用于细微之处,使负荷和耗电量走势基本上呈现同样的曲线走势。

*DVFS(dynamic voltage and frequency scaling)=在LSI中,通过根据处理负荷等动态控制电源电压和工作频率,从而削减耗电量的方法。以LSI根据软件指示变更设定的形态运行。

从细微之处入手,瑞萨移动的做法可谓典型。该公司的母公司瑞萨电子在用于传统手机的应用处理及基带处理整合型处理器"SH-Mobile G"系列中,将DVFS应用到了CPU内核中,并对电源域和时钟系统进行了细分化。

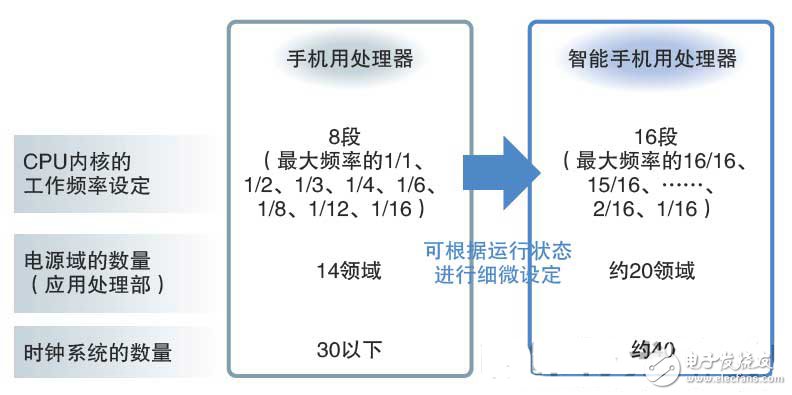

而瑞萨移动面向智能手机开发的"MP5232"则对CPU内核的工作频率设定以及电源域和时钟系统则进行了更加细致的划分(图7)。"由于必须配置电源开关,因此并不是只要细分就完事了。我们设想了智能手机的使用情况,找到了最佳划分点"(瑞萨移动移动多媒体事业本部SoC事业部事业部长服部俊洋)。

图7:根据利用情况对电力进行极其细微的控制

瑞萨移动面向智能手机开发的"MP5232"与用于传统手机的处理器相比,可以根据利用情况对电力进行极其细微的控制。CPU内核的工作频率设定、电源域的数量以及时钟系统的数量均大幅增加。

对每个CPU内核控制频率

美国高通的"Snapdragon"系列采用根据多个CPU内核进行DVFS的方式。向一个内核施加较大负荷时,如果其他内核的负荷较小,则会削减负载较小的内核的工作频率

- 单片式电池充电器简化太阳能供电设计(08-20)

- 能量收集器于所在环境产生电能,无线传感器无需使用电池(08-23)

- 嵌入式软件电源能耗优化的解决方案(10-21)

- 利用LTC6801进行电池管理系统 (BMS) 的故障监视(10-19)

- 电动 / 混合电动汽车电池管理系统的可靠性(11-09)

- VRLA 蓄电池在光伏发电系统中的研究与应用(02-09)