基于赛灵思FPGA的空间电场信号采集系统的设计和实现

码:A/D控制程序、例化FIR的IP核产生数字滤波器、同步422发送程序。FPGA内部的工作流程图如图2所示。

图2 FPGA内部工作流程

2.1 FPGA对AD1610采样的控制

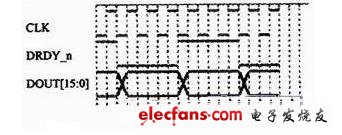

当不使用ADS1610的时候,可以把nPD引脚置低,这样就关掉了ADS1610的电源,在设计中将nPD引脚置高。ADS1610为并行数据传输,在数据准备就绪之后,需要保持时间来确保上一组数据有效,经过建立时间之后开始接收下一组数据,时序图如图3所示。

图3 ADS1610工作时序图

引脚nSYNC可以用来同步多片.ADS1610,单片设计时为复位引脚,这里设计不采用多片同步,将nSYNC置低时,ADS1610是异步复位的。当复位的时候,所有的数字电路清零,16位输出引脚DOUT[15:0]被全部置为低,而数据就绪引脚nDRDY被置为高。在程序的设计中,nSYNC在时钟信号的下降沿拉高,则nDRDY在接下来的第二个时钟上升沿拉低。

2.2 数字滤波器的实现

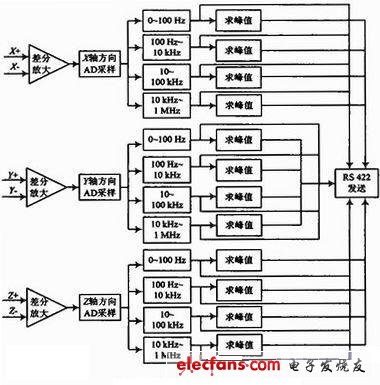

借助Matlab中的滤波器设计和分析工具FDATool,其操作简单、灵活,用户只需在GUI中输入设计需要的滤波器各项参数,就可以获得需要的数字滤波器。本设计中共划分为4个频段:0~100 Hz,100 Hz~10 kHz,10~100 kHz,100 kHz~1 MHz,经实验发现,频带宽度过大的带通滤波器性能不是很理想,通带内幅度并不平坦,失真较大。因此除了第一个频段采用低通滤波器外,另外三个频段采用低通滤波器+高通滤波器的方法来实现,如频带为100 Hz~10 kHz可以用截止频率为10 kHz的低通滤波器和100 Hz的高通滤波器相加得到。将生成的FIR滤波器系数.coe文件导入4个Xilinx ISE中的IP核中,分别例化生成四个FPGA片内的数字滤波器,对X,Y,Z三个方向采集到的电场信号进行频段的划分。

2.3 同步422

将X,Y,Z每个方向的各个通道的滤波后的信号,加上包头、时间码、通道号、校验码之后通过422芯片DS26LV31AT、发送给后端的设备。主要包括两个子模块:波特率产生模块和发送模块。

波特率产生模块:系统外接18.432 MHz晶振,用来产生同步422通信所需要的115 200 b/s的波特率。本模块采用10 MHz时钟。波特率的计算:(1/115 200)/(1/1×107)=86个系统时钟周期,为得到50%占空比的波特率时钟,使得计数器在计数到86/2=43时将输出置高,之后在计数到86时将输出置低并重新计数,就可实现所需波特率的时钟;发送模块:采用状态机进行编写,由五个状态(IDLE,WAIT,STAR T,SHIFT,STOP)和一个进程组成。

3 系统实现

本设计系统硬件设计采用Altium Designer 6.0绘制原理图和PCB图,FPGA程序设计则是在Xilinx ISE 11和Modelsim SE 6.5e平台上设计和仿真,滤波器系数则是在Matlab中的FDA tools工具箱中生成并导入ISE中的有限脉冲响应的知识产权核中。

图4 采样频段方框图

在系统的输入端加入-3~3 V的模拟输入电压进行测试,进行FPGA片上数据采集处理实验,在每个模块的输出端添加测试焊点,方便逐步调试。系统设计框图如图4所示,根据后端收到的实验数据对比可知,本系统设计完成了设计要求。

4 结语

本文提出的基于FPGA的空间电场信号采集系统应用于探空火箭有效载荷——箭载电场仪探头后端信号采集与处理部分,也可以为地面电场仪处理电场信号提供服务。该方案解决了电场信号采集系统设计要求,避免了模拟滤波电路易受温度、噪声等影响,硬件电路大大简化,可调适性好。经过实践证明本设计方法设计正确,减轻了设计者对于庞大模拟电路的设计负担,系统运行稳定可靠,可移植性强,可用于多种数据采集电路的设计,有一定的参考价值。

- 基于计算机的测量仪器的内部和外部校准(10-08)

- 基于AD73360和TMS320F2812的数据采集系统设计(12-06)

- 基于暂态行波法的配电网故障定位装置研究(02-01)

- 数据采集处理系统在电力中的应用设计(12-30)

- 如何通过整合众多特点和性能来解决数据采集兼容性问题(09-15)

- VC串口通信的数据采集系统设计(10-09)