基于Altera CPLD的水轮发电机组转速监控系统的设计

4 kBROM,256 BRAM。不用附加任何外围电路即可工作,有效地节省了配置电路板的面积。F1121单片机支持多电压工作,可以使配置板适应不同的工作电压。F1121 的FLASH型主存储器,通过JTAG控制器可以实现程序代码的下载,实现运行控制和在系统编程。

4 系统功能的VHDL描述

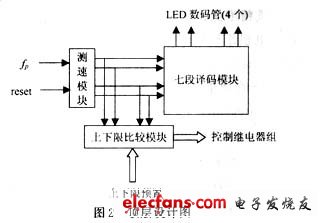

本系统的顶层设计由3个子模块组成,顶层设计图如图2所示。

下面给出测速模块和7段译码模块的VHDL描述,至于上下限比较模块,可根据预置值及具体的控制需要,编制相应的VHDL程序,使模块输出要求的控制信号。4.1测速模块模块说明:fp为光电传感器的输出脉冲,reset是8复位端子,speed0,speed1,speed2,speed3分别为脉冲计数的个位、十位、百位、千位的BCD码输出,c1,c2,c3分别为个位向十位、十位向百位、百位向千位的进位。

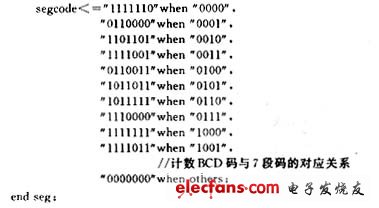

4.2 7 段译码模块

7 段译码模块说明:speed0,speed1,speed2,speed3分别为脉冲计数的个位、十位、百位、千位的BCD码输出,作为7段译码模块的输入,segcode0,segcode1,segcode2,segcode3分别为个位、十位、百位、千位的7段字段码输出。7段译码模块的 VHDL语言描述如下:

5 结语

本设计的VHDL程序在Altera公司的MAX+PLUS Ⅱ(Multiple Array Matrix and ProgrammableLogic User System)CPLD设计开发工具上进行编译仿真,较好地完成了设计要求的功能。在本系统的设计中,由于CPLD及EDA开发工具的使用,大大简化了硬件电路,降低了产品成本,缩短了设计周期,提高了系统的可靠性和灵活性。

VHDL 发电机 Altera CPLD CMOS 相关文章:

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于Max+PlusⅡ与VHDL的数字电压表设计(08-26)

- 基于VHDL和CPLD的智能数字电压表设计(10-09)

- 基于Multisim的VHDL建模与仿真(09-25)

- 基于FPGA的等精度频率计的设计与实现(11-03)

- 基于MC8051 IP核和FPGA的频率计设计(11-24)