基于Altera浮点IP核的浮点矩阵相乘运算的实现和改进设计

图3在全局同步信号时钟sysclk、复位reset、使能enable的作用下,当calcmatrix信号为‘1’时,开始计算并生成输出控制信号。其中a_cntrl部分用于控制矩阵A数据加载模块,主要包含地址信号readaa和锁存信号latchaa,来一个锁存高电平则存储A矩阵数据readaa;b_cntrl部分则对应于矩阵B的控制,输入B矩阵数据readbb;cache部分用于控制数据缓存部分串行输入并行输出,包含着相应的读地址信号cacherdadd、写地址信号cachewradd、cache选择信号cachemesel,三者同步控制并行输出;outcntrl部分是整个系统的输出控制部分,在准备信号ready之后,出现outvalid高电平,表示输出数据有效,同时完成信号done为低电平。为使矩阵A、B数据能同时加载到浮点乘加模块上,需要使一个readaa值对应于readbb的columnsbb个数据。在本设计中使用的是A9×16数据与B16×8数据进行计算,生成的outvalid有9个脉冲,每个脉冲包含8个矩阵输出数据。

对于A、B矩阵的数据加载,采用的是串行输入并行输出的控制器,由移位寄存器组成,当计数器计数到端口输出值时(如端口并行输出8个数则计数到8),并行输出数据。

浮点乘加模块采用并行相乘、并行相加的方式。由于考虑到精度问题,采用浮点位数转换,将32 bit的输入数据进行浮点扩展为42 bit,再进行乘加运算,最后再将42 bit数据转换为32 bit数据。采用三级流水线的方式,进行并行乘加运算,提高设计系统性能。

在双口RAM组的实现上,是将一组simple dualport ram[3]并列成一个RAM组。输入由矩阵A、B的数据信号和ROM输出的地址信号组成;输出就是一路矩阵A数据和一路矩阵B数据,数据深度与vectorsize等同。其中每一个RAM的深度为rowsaa×columnsbb/vectorsize,保证数据的可重用性,同时相对应的ROM中存储的地址信号分别为:

A:1 2 1 2 3 3 1 2 3 4 4 4 1 2 3 4 5 5 5 5 1 2 3 4 5 6 6 6 6 6 ……

B:1 1 2 2 1 2 3 3 3 1 2 3 4 4 4 4 1 2 3 4 5 5 5 5 5 1 2 3 4 5 ……

以此类推即可得到相应的地址信号查找表。

在数据缓存模块的设计上也采用串行输入并行输出的方式。使用移位寄存器的方式实现,在并行浮点相加部分类似于上述的并行乘加[4]计算,采用多级流水线并行相加的方式完成。

3.2 计算结果仿真

对改进的设计进行仿真,采用A9×16数据与B16×8数据相乘,获得计算结果仿真如图4所示。

![]()

从图4可见,loadaa、loadbb、calcimatrix三者的时序满足浮点矩阵运算的时序要求,在前两者数据加载后,加载calcimatrix上升沿,进行矩阵相乘。在outvalid为高电平时输出数据,同时完成信号done输出低电平。在输出结果上,共分为9个大组,各大组有8个数据,共组成72个数据结果,其中显示了第一部分输出结果,获得与Matlab仿真相近的计算结果,在精度上相差不到万分之一。

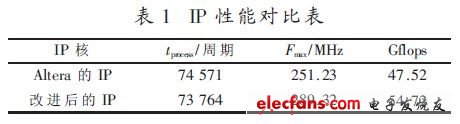

从表1中可以看出,改进后的IP核在处理时间上缩短了807个周期,同时在最高运行时钟上提升了15%,系统整体的持续性能增加了7.2 Gflops。

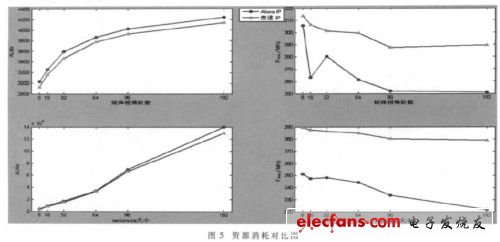

依据改进前后的IP核,使用Quartus9.1软件进行综合布局布线,映射到Stratix Ⅲ EP3SE110F780C2器件中,可获得相应的资源对比图如图5所示。由于采用的都是并行浮点乘加运算,所以在乘法器资源的消耗上不变;同时由于只是在存储器的存储方式上作出变动,所以二者的存储资源相等。从而只需要对图中显示的矩阵阶数、vectorsize大小进行比较即可,而浮点计算性能与最高时钟频率变化方向相同,所以只对ALM数量及最高时钟频率进行对比。

从图5中资源消耗对比可见,当设定vectorsize为固定值8(图5左半部)时,随着矩阵阶数的增加,改进后的IP核在ALM资源消耗上较改进前数量上有一定的减少,在最高时钟频率上都有小幅度提升,这是因为矩阵输入时消耗时间过长;当设定矩阵阶数为192×192(图5右半部)时,随着vectorsize值的增加,改进后IP核在ALM数量上有所减小,在最高时钟频率上则有小幅度提升,且波动幅度在3.4%左右。可见,改进后IP核比原Altera的IP核综合性能有所提升。

- 一种消防应急灯具专用控制芯片的设计(11-02)

- 基于FPGA的8段数码管动态显示IP核设计(02-03)

- 基于FPGA和IP Core的定制缓冲管理的实现(08-14)

- 基于Altera ASI IP核的ASI发送卡实现(02-25)

- FPGA的高速多通道数据采集控制器IP核设计(04-22)

- 基于EDA或FPGA的IP保护的实现(09-16)