基于SPB16.X平台的小型化设计实现与应用

1.引 言

产品小型化的好处是显而易见的,从而带动了小型化设计技术的发展。这些技术主要有:

传统意义上的HDI技术,经过多年的发展,现在国内厂家可以做到3+n+3,也就是3阶盲埋孔设计已经开始逐步成熟了。

ANYLAYER(任意阶)技术,又叫任意过孔技术(ALIVH-Any Layer IVH Structure MulTIlayer Printed Wiring Board),随着苹果的iPhone 4及iPad采用了ANYLAYER HDI,任意阶技术也因此越来越被广大智能手机等厂家所关注

埋阻、埋容和埋入式元器件,不少厂家研究埋阻、埋容技术多年,埋容也已经能实现量产,埋入式元器件早些年大量用于航空航天和军事领域,这些年因为SiP的普及,在普通电子产品领域也开始火起来,算是比较新的技术,多用于封装载板

小型化技术的推广,除了对生产工艺带来巨大的挑战之外,还对设计方法、观念、工具等都带来深远的影响。传统的设计工具效率低下,并且因为不具备相应的约束规则而需要大量人工干预检查,比较容易出错,设计工程师需要全新的支持小型化设计技术的工具。Cadence SPB16.5全面加强了对小型化设计的支持,增加了埋入式元器件的设计方法,同时进一步优化增强了对HDI以及ANYLAYER技术的支持。

2.HDI技术以及工艺实现

HDI:High Density Interconnect,高密度互连。传统的PCB板的钻孔由于受到钻刀影响,当钻孔孔径达到0.15mm时,成本已经非常高,且很难再次改进。而 HDI板的钻孔不再依赖于传统的机械钻孔,而是利用激光钻孔和机械钻孔的结合应用。HDI也就是通常我们所说的盲埋孔技术。HDI技术的出现,适应并推进了PCB行业的发展。使得在PCB板内可以排列上更加密集的BGA、QFP等。

HDI的分类

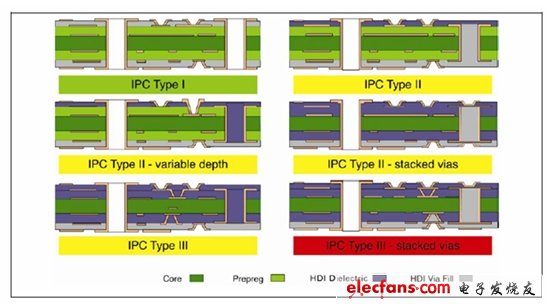

IPC-2315上对HDI的分类有详细说明,这里我们按照激光孔深度的不同分为以下几种:一阶HDI, 二阶HDI 三阶HDI,如图1所示。

图1:HDI的分类

一阶的HDI技术是指盲孔仅仅连通表层及与其相邻的次外层的成孔技术。通常激光孔和盘采用4/12mil(5/12mil),当然,现在也可以采用更小盘如 4/10mil了应对密度较高的布线。内层的盲孔我们一般采用普通孔。而二阶的HDI技术是在1阶的HDI技术上的改进和提高,它包含激光盲孔直接由表层钻到第三层(2+N+2),和表层钻到第二层再由第二层钻到第三层两种形式(1+1+N+1+1),其加工难度远远大于1阶的HDI技术。三阶HDI板的加工制作工艺与二阶基本相似,就是多了几种类型的孔。目前国内的二阶HDI设计和加工已经非常成熟了。

3.HDI板设计上的挑战

多阶HDI的设计,需要一个灵活强大的约束管理器,能识别微孔和普通机械孔,能设置微孔与其他元素的间距约束。同名网络的约束关系变得复杂,需要支持各种情况下的同名网络间距约束检查。需要能清晰的显示不同类型的过孔信息,方便设计工程师进行管理。Allegro的3D结构视图可以帮助我们更加了解不同孔的结构。

Cadence的 SPB16.X平台,具有强大的HDI设计功能。

首先是Micro Via属性,使得HDI工艺实现的微孔彻底和传统机械实现的盲埋孔区分开来,单独进行约束设置;结合单独区分出来的同名网络设计约束、盘中孔设计约束等,实现了灵活强大的约束驱动的HDI设计。

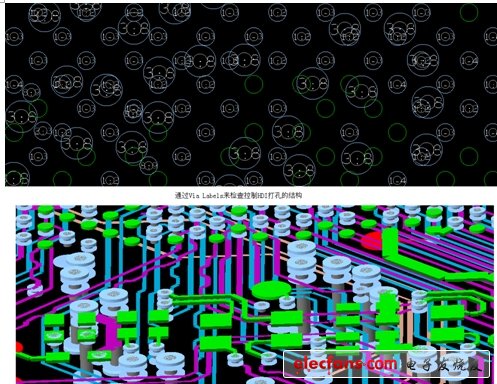

Via Labels功能,可以让设计者更加方便的查看了解微孔所连接的层,进行设计规划;同时结合基于OpenGL的3D过孔结构现实功能,从平面到立体,帮助工程师实现复杂的多阶过孔结构管理。

无盘设计功能可以自动根据走线层来实现通孔焊盘的存在与去除,实现了设计之初就因为去除焊盘来实现更加优化的布线空间利用率;与之相匹配的功能是增加了Hole和其他元素的间距约束设置。

其他功能包括:DRC Modes里面的Via in Pad约束设置,过孔类型的结构示例图形,强大的Fan out功能和BGA出线功能等

一博科技采用Cadence强大的小型化设计工具,结合自身HDI的设计和加工能力,完美完成了多个密度极高的小型化产品设计任务。

图 2是一个3阶HDI的案例,一博科技借助Cadence的设计平台以及在HDI设计领域多年的经验,完美的完成了设计。同时由于密度原因,设计的最小线宽和间距达到了2.4mil ,挑战了业内的极限。一博科技借助自有板厂和合作厂家在HDI生产加工上的领先工艺能力,帮助客户完成了制板和贴片。

图2: 3阶HDI的案例

4.ANYLAYER(任意阶)技术

近些年来,为了满足一些高端消费类电子产品小型化的需要,芯片的集成度越来越高,BGA管脚间距越来越近(小于等于0.4pitch),PCB的布局也越来紧凑,走线密度也越来越大,为了提高设计的布通率且不影响信

- PCB布线技术中的抗干扰设计(03-08)

- 基于Protel 99 SE环境下PCB设计规范与技巧的研究(08-30)

- 高速PCB可控性与电磁兼容性设计(11-18)

- 分布电容在EMC/EMI之设计中的应用(01-11)

- LED开关电源的PCB设计规范(06-12)

- LED开关电源的PCB设计分析(09-06)