基于AD9851的信号发生器设计

时间:04-02

来源:《山西电子技术》

点击:

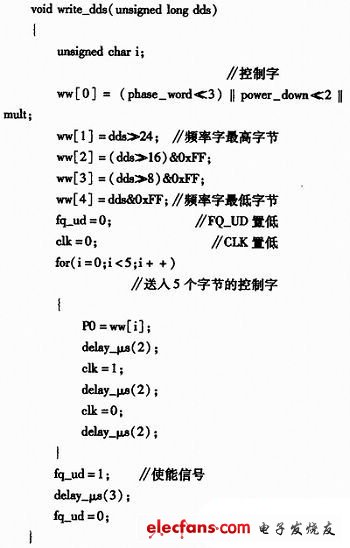

完成W_CLK和FQ_UD置低电平的工作;然后依次把5个频率控制字发送出去;在发送数据时,必须严格把握工作时序。tds是数据的建立时间,tdh是数据的保持时间,twh和twl分别是W_CLK的高电平和低电平的持续时间,根据手册可知,以上4个时间至少为3.5ns.由于S52单片机的晶振比较低,满足工作时序没有问题。

DATA在W_CLK上升沿到来时有效。

写频率控制字的子程序如下:

4 系统测试

下面是AD9851设置输出不同频率时,通过100MHz泰克示波器观察到波形图,如图6所示。通过其波形图,可以看出,DDS的输出频率在60 MHz以下十分精确和稳定,波形比较完美,频谱比较干净。设计频率在70 MHz时,波形失真越严重,频谱的各次谐波逐渐增多。并且DDS正弦输出的幅度随频率增高而下降。低频端约1Vpp,高频端约200mVpp,实际应用中应外加合适的宽带放大器。

- 低频正弦信号发生器的设计(02-15)

- 基于CPLD和LVPECL的可调窄脉冲信号发生器设计与实现(11-13)

- 一种新型的正弦信号发生器的设计与实现(04-23)

- 基于SLH89F5162的信号发生器设计(02-24)

- 基于DDS芯片的全数控函数信号发生器的设计与实现(06-24)

- 什么是信号发生器?信号发生器的使用方法,信号发生器各种干货知识(04-09)