基于AD9851的信号发生器设计

引言

直接数字合成(Direct Digital Synthesis-DDS)是近年来新的电子技术。DDS系统一个显着的特点就是在数字处理器的控制下能够精确而快速地处理频率和相位。除此之外,DDS的固有特性还包括:相当好的频率和相位分辨率(频率的可控范围达μHz级,相位控制小于0.09°),能够进行快速的信号变换(输出DAC的转换速率百万次/秒)。

基于直接数字频率合成(DDS)原理,采用AD9851型DDS器件设计一个信号发生器,实现50 Hz~60 MHz范围内的正弦波输出。通过功率放大,在50Ω负载的情况下,该信号发生器在50 Hz~10 MHz范围内输出稳定正弦波,电压峰峰值为0~5V±0.3V.

1 AD9851集成芯片简介

AD9851是在AD9850的基础上,做了一些改进以后生成的具有新功能的DDS芯片。AD9851相对于AD9850的内部结构,只是多了一个6倍参考时钟倍乘器,当系统时钟为180MHz时,在参考时钟输入端,只需输入30 MHz的参考时钟即可。AD9851是由数据输入寄存器、频率/相位寄存器、具有6倍参考时钟倍乘器的DDS芯片、10位的模/数转换器、内部高速比较器这几个部分组成。其中具有6倍参考时钟倍乘器的DDS芯片是由32位相位累加器、正弦函数功能查找表、D/A变换器以及低通滤波器集成到一起。这个高速DDS芯片时钟频率可达180MHz,输出频率可达70 MHz,分辨率为0.04Hz.

AD9851可以产生一个频谱纯净、频率和相位都可编程控制且稳定性很好的模拟正弦波,这个正弦波能够直接作为基准信号源,或通过其内部高速比较器转换成标准方波输出,作为灵敏时钟发生器来使用。

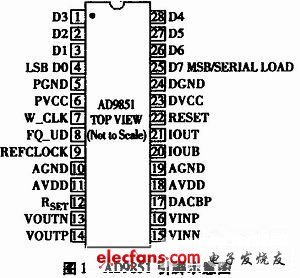

AD9851的各引脚功能如图1所示。

D0~D7:8位数据输入口,可给内部寄存器装入40位控制数据。

PGND:6倍参考时钟倍乘器地。

PVCC:6倍参考时钟倍乘器电源。

W-CLK:字装入信号,上升沿有效。

FQ-UD:频率更新控制信号,时钟上升沿确认输入数据有效。

FREFCLOCK:外部参考时钟输入。

CMOS/TTL脉冲序列可直接或间接地加到6倍参考时钟倍乘器上。在直接方式中,输入频率即是系统时钟;在6倍参考时钟倍乘器方式,系统时钟为倍乘器输出。

AGND:模拟地。

AVDD:模拟电源(+5 V)。

DGND:数字地。

DVDD:数字电源(+5 V)。

RSET、DAC:外部复位连接端。

VOUTN:内部比较器负向输出端。

VOUTP:内部比较器正向输出端。

VINN:内部比较器的负向输入端。

VINP:内部比较器的正向输入端。

DACBP:DAC旁路连接端。

IOUTB:"互补"DAC输出。

IOUT:内部DAC输出端。

RESET:复位端。低电平清除DDS累加器和相位延迟器为0 Hz和0相位,同时置数据输入为串行模式以及禁止6倍参考时钟倍乘器工作。

2 系统硬件设计

2.1 设计方案

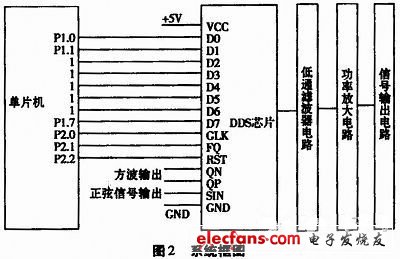

本设计方案采用AD9851芯片的并行数据模式,系统框图如图2所示。系统包含单片机电路、AD9851芯片、低通滤波器电路、功率放大电路以及信号输出电路共5部分。其中单片机电路部分选用通用的51系列单片机AT89S52,外部晶振频率为12 MHz.低通滤波器电路选用无源滤波器来进行设计,由于本设计最高输出频率为30 MHz,所以低通滤波器的截止频率在40 MHz左右。基准时钟采用贴片封装30.000 0 MHz有源晶振,为AD9851芯片提供高稳定度,高精确度的信号源。

2.2 低通滤波器电路的设计

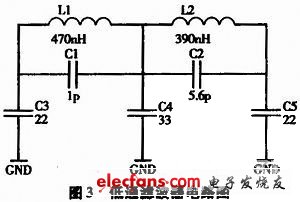

低通滤波器电路采用2阶LC椭圆低通滤波器,能有效抑制DDS的输出杂散。电路如图3所示。

2.3 功率放大电路的设计

功率放大电路采用AD828宽频带运放芯片。AD628内部集成两个运算放大器,供电方式有双电源供电和单电源供电两种,特别适合于高频信号的变换与传输。本设计中为了提高信号峰峰值的输出幅度,芯片电源采用双电源正负10 V直流电源。这样可以保证在10 MHz的带宽内得到一个相对较高的电压幅度。

3 系统软件设计

3.1 AD9851的复位工作时序

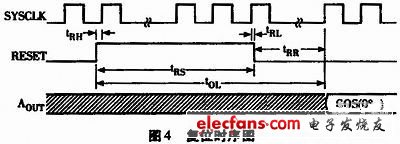

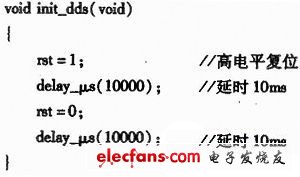

AD9851的复位时序如图4所示。从时序可以看出,AD9851芯片复位的条件是在RESET引脚出现一个高电平,并持续时间至少为trs.根据手册提供的时间参数,可知道trs最短时间是5个系统时钟,没有时间上限。由于系统电路中,单片机的晶振采用12 MHz.执行一条指令所需要的时间是1μs,为了保证复位时序的可靠性,采用复位的时间为10ms.

具体复位子程序如下:

该子程序中用到delay_μs()延时程序延时约1μs.

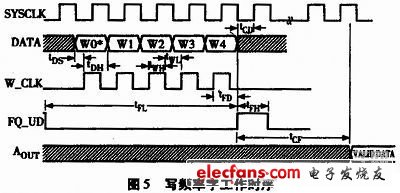

3.2 写频率字的工作时序

写频率字的工作时序是AD9851芯片的关键时序,它关系着信号发生器功能的实现。并行模式下,写频率字的工作时序如图5所示。

由时序图,可以看出:

在输出频率控制字之前。必须

- 低频正弦信号发生器的设计(02-15)

- 基于CPLD和LVPECL的可调窄脉冲信号发生器设计与实现(11-13)

- 一种新型的正弦信号发生器的设计与实现(04-23)

- 基于SLH89F5162的信号发生器设计(02-24)

- 基于DDS芯片的全数控函数信号发生器的设计与实现(06-24)

- 什么是信号发生器?信号发生器的使用方法,信号发生器各种干货知识(04-09)