一种高速PCI数据采集卡设计方案

时间:03-24

来源:本站整理

点击:

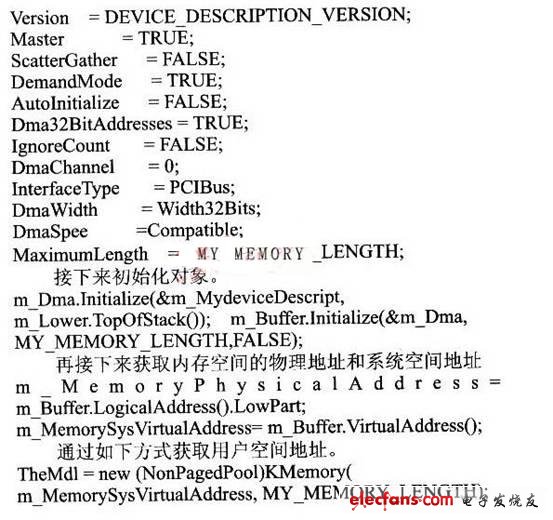

述符结构体m_MiydeviceDescript,设备描述符结构体各个域的设置如下:

将UserSIpaceAddress传递给应用程序,则应用程序就可以访问存放数据的内存空间了。

FPGA在每传送给CY7C09449一块2k双字的数据后就通过CY7C09449的引脚IRQ_IN向主机发送中断请求。在主机的中断服务程序中用m_Me-morjPhyPhysicalAddress设置CY7C09449的DMA3E机物理基地址寄存器,然后设置DMA局部基地址寄存器、DMA长度寄存器来配置数据传输的源地址地址和数据长度,然后再写CY7C09449的DMA控制寄存器来启动DMA传输。在所有数据块传输完毕,主机中断服务程序发送给应用程序一个消息,这时应用程序就可以通过UserSpaceAddress访问接收到的数据了。

5 结论

在高速数据采集卡的设计中FPGA对局部总线的控制逻辑由于采用了同步数据传输控制方式使得局部总线的最高传输速度可达200Mb/s。在WindowsXP下的驱动程序设计使用了DMA数据传输方式,提高了数据存储速度。高速数据采集卡可以达到80Mb/s的数据采集速度,设备运行稳定,达到了设计要求。

- 一种高精度中频信号数据采集卡的硬件设计(04-14)

- LT3751如何使高压电容器充电变得简单(08-12)

- 三路输出LED驱动器可驱动共阳极LED串(08-17)

- 浪涌抑制器IC简化了危险环境中电子设备的本质安全势垒设计(08-19)

- 严酷的汽车环境要求高性能电源转换(08-17)

- 适用于工业能源采集的技术 (08-10)