基于FPGA的RS232异步串行口IP核设计

数据采集系统常需要进行异步串行数据传输。目前广泛使用的RS232异步串行接口,如8250、 NS16450等专用集成器件,虽然使用简单,却占用电路板面积、布线复杂等缺点。片上系统SoC(System on Chip)是以嵌入式系统为核心,以IP复用技术为基础,集软、硬件于一体的设计方法。使用IP复用技术,将UART集成到FPGA器件上,可增加系统的可靠性,缩小PCB板面积;其次由于IP核的特点,使用IP核可使整个系统更加灵活,还可根据需要实现功能升级、扩充和裁减。这里采用VHDL语言编写 UART模块,将其集成到FPGA上,与器件其他功能模块构成片上系统SoC。

2 异步串行口模块设计与实现

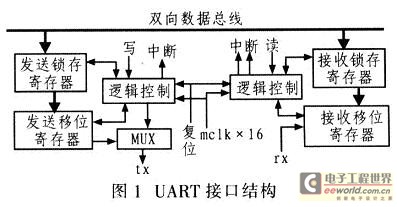

2.1 UART结构

图1为完整的UART接口,包括由发送锁存器、发送移位寄存器和逻辑控制组成的发送模块(txmit),以及由接收锁存器、接收移位寄存器和逻辑控制组成的接收模块(rxcver)。发送模块和接收模块除共用复位信号、时钟信号和并行数据线外,各自分别有输入输出和逻辑控制单元。

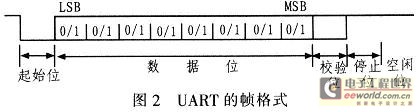

2.2 UART的帧格式

图2为UART的帧格式。该帧格式包括线路空闲状态(idie,高电平)、起始位 (start bit,低电平)、5~8位数据位(databit)、校验位(parity bit,可选)和停止位(stop bit,位数可为1、1.5、2位)。该格式是由起始位和停止位实现字符同步。UART内部一般有配置寄存器,可配置数据位数(5~8位)、是否有校验位和校验的类型、停止位的位数等设置。

2.3 波特率时钟的控制

由于数字量接口、工作模式选择、实时监测接口的波特率都不同,UART核包含一个可编程的波特率发生器,可灵活配置波特率。波特率发生器给发送模块和接收模块提供发送数据和接收数据的基准时钟,波特率发生器产生的时钟mclkx16是串行数据波特率的16倍。它对系统时钟n分频,n=系统时钟/波特率&TImes;16,针对不同波特率设定相应数值可得到所期望的波特率时钟。 <script type=text/javascript>funcTIon ImgZoom(Id)//重新设置图片大小 防止撑破表格

{

var w = $(Id).width;

var m = 650;

if(w< m){return;}

else{

var h = $(Id).height;

$(Id).height = parseInt(h*m/w);

$(Id).width = m;

}

}

window.onload = funcTIon()

{

var Imgs = $("content").getElementsByTagName("img");

var i=0;

for(;i

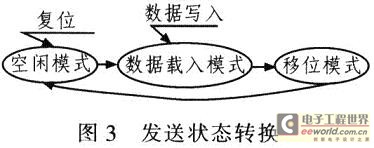

2.4 发送模块设计

发送模块分为空闲、载入数据、移位等3种模式。如图3所示。当并行8位数据从总线写入发送模块后,发送模块将并行数据装入锁存器thr中,然后在移位寄存器tsr中将数据移位,产生完整的发送序列(包括起始位,数据位,奇偶校验位和停止位),以相应波特率从tx发送。发送模块的输入时钟mclkx16是串行数据波特率的16倍,模块内部将其16分频后得到波特率时钟txclk。

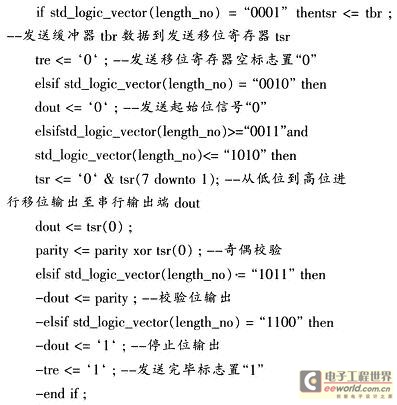

发送模块部分VHDL程序如下:

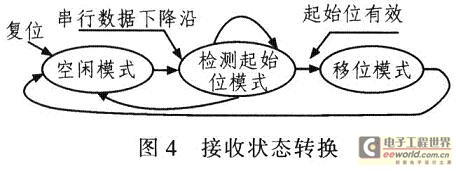

2.5 接收模块设计

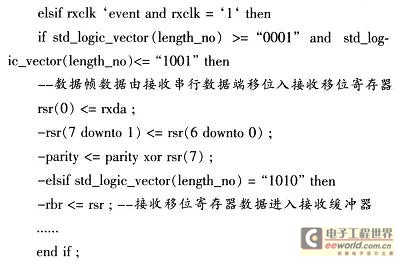

接收模块也分为空闲、检测起始位、移位等3种模式。如图4所示。首先捕捉起始位,在 mclkx16时钟下不断检测从rx端输入数据的起始位,当检测到起始位后,接收模块由空闲模式转换为移位模式,并且16分频mclkx16产生 rxclk波特率时钟。此时rxclk时钟的上升沿位于串行数据每一位的中间,这样接下来的数据在每一位的中点采样。然后由rxclk控制在上升沿将数据位写入移位寄存器rgr的rsr[7]位,并且rsr右移1位,依次将8位数据全部写入rsr,并且停止产生rxclk波特率时钟。判断奇偶校验、帧结构和溢出标志正确后,rsr寄存器中的数据写入rhr数据锁存寄存器中,最后由8位数据总线输出转换完成的数据。

接收模块部分VHDL程序如下:

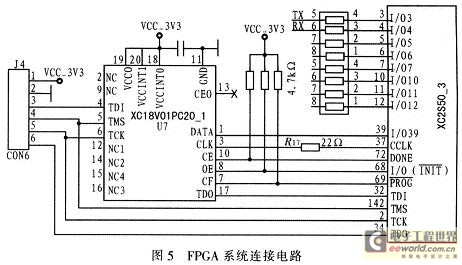

3 硬件电路设计

UART IP核设计完成后需要嵌入FPGA系统中才能运行,该系统选用Xilinx公司Spartan-IIE XC2S50型FPGA和与其配套的EPROM XC18V01组成,如图5所示。该系统已实现设计要求的功能,实现IP核的验证。

4 结果分析

程序经仿真验证后,须综合生成IP核并嵌人FPGA中。使用Xilinx公司的Xilinx ISE工具综合UART模块,FPGA选用Xilinx公司Spartan-IIE XC2S50,系统时钟40 MHz。经Xil-inx ISE后,资源使用结果如表1所示。表明使用少量FPGA的Slice和LUT单元就可生成UART核,节省资源UART核可灵活分成接收和发送两部分,可根据需要选择使用。节省系统资源;一些控制标志字也可根据需要自行删减和扩充。最后将集成有UART核的FPGA数据采集系统与测试台进行异步串行通信实验,检测通信数据表明使用UART核传输数据稳

- 基于PCI-9846H的死区时间引起的电压波形畸变的研究(11-10)

- 一种多处理器数据采集系统方案(03-24)

- 基于USB2.0和DDR2的数据采集系统设计(03-19)

- 基于MSP430和USB的数据采集系统(04-14)

- 基于LabVIEW的光谱数据采集与分析(02-12)

- 史上最牛:一款高性能低功耗数据采集系统的设计详解(07-22)