智能微网保护装置新平台技术设计

量的每个变位都有精确到微妙的记录,随时可以上送到主控制器;开出量的数据报文需要经过奇偶校验,在硬件上受到单独的出口电源控制,双重闭锁保证了安全性。

3、软件逻辑

3.1 面向对象软件平台

为保证程序系统化以及可延续性,且为应用开发提供安全、灵活、一致的编程接口,建立了基于多任务实时操作系统Vxworks,采用面向对象设计方式的适用各种开发环境、具有长生命周期的软件平台。该平台可以大大缩短应用开发周期,支持电力行业各种标准通信规约,如IEC103、IEC104、IEC61850等等。

软件平台的基本元素称为元件,在面向对象思想中,是将数据以及定义在数据上的操作封装在一起的过程,同样也可以扩展为一个个智能化插件,将同类的应用程序以元件的形式进行封装,可以提高代码的可维护性和可重用性。

软件平台的组成有:各个插件上的系统程序、底层的驱动程序、智能插件上的功能程序和后台配置工具软件等。系统程序包括定值调用与存储功能模块、事件记录与录波功能模块、系统监测与自检功能模块、定时器控制功能模块等;驱动程序包括操作系统接口功能模块、插件识别与注册功能模块、各种硬件控制功能模块等;智能插件功能程序包括开入开出逻辑控制、参数管理功能模块、报文收发与拼接功能模块等;后台配置工具包括文件、程序的上传下载功能模块、定值参数的调取与修改功能模块、记录和波形的查看和分析功能模块等。

3.2 MLVDS总线逻辑设计

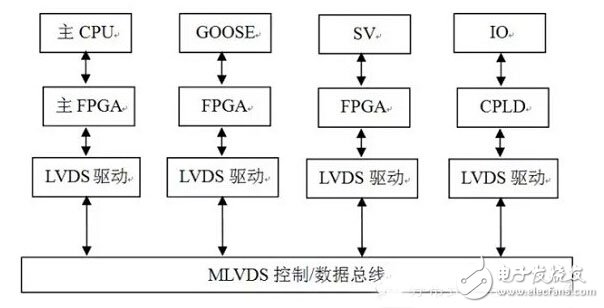

装置上电时主处理器读取配置文件,得到智能插件数量与类型,其中插件数量根据工程不同可灵活增减,用配置工具进行注册。受到总线板插槽数量限制,插件数量最大为16块,一致的软硬件接口可根据工程需求配置不同的插件。MLVDS总线结构如图2所示。

图2 MLVDS总线结构图

MLVDS总线分为控制总线与数据总线。控制总线用于调配轮询插件,由主处理器插件上的FPGA产生定时中断,根据不同插件的数据量分配不同的时间,再召唤该插件数据。插件在轮到自己发送时才可以发送,如果有内容则发送信息,如果无内容则发送空帧;在其它插件发送时处于监听状态,如果发现是发给自己的开启接收逻辑,否则不予理会。总线控制逻辑可以保证所有插件受到主机调配,相互间不会产生竞争或冲突的情况。

4、结论

基于集中式保护方式研发的智能微网保护装置目前已通过了型式试验和动模试验的检测,检测结构表明了该装置的保护功能以及各项软硬件指标均满足或高于电力行业标准,具有抗干扰能力强、测量精度高、反应速度快速、应用场合广泛等特点。

本文提出的智能微网保护装置的新平台技术方案,可广泛应用于不同的小系统,具有实际操作性。该平台软硬件资源丰富,保护功能强大,配置可随需求裁剪,可靠性极高,可以满足微网保护装置的各种功能需求,具有良好的应用前景。

- 管理多电压轨系统让数字电源管理变得简单(08-17)

- 具USB OTG和过压保护的紧凑型电源管理器(08-17)

- 设计切实可行的压电能和热能收集方案需考虑的因素(08-23)

- 针对能量收集型无线远程传感器网络的实用电源管理设计(11-29)

- ACPI PC电源管理(05-13)

- 具有USB OTG和过压保护的紧凑型电源管理器的实现(10-17)