基于DSP的车载导航系统硬件电路设计与实现

力30 mA,需光耦隔离,设置两个16位计数器和1位状态寄存器,分别记录里程计脉冲输入和状态信息,里程计脉冲上升沿触发计数,中断5锁存;要求行车状态信号State可用命令使能和禁止,使能状态下当State=1时,里程计信号加法计数;当State=0时,减法计数;禁止状态下里程计信号加法计数,里程计信号先经RC滤波电路和保护二极管,然后经光隔进入FPGA。

状态检测信号包括3路跳模检测信号、3路高压状态信号和3路机抖状态信号,信号形式均为开关量,幅值为TTL,机抖状态信号和高压状态信号需光耦隔离。跳模检测信号处理形式和参数选择与加速度计信号相同;高压状态信号和机抖检测信号处理形式则与陀螺信号一致。

测温信号包括10路测温电阻输入和1路测温电阻输入公共端,温度范围在-45~+70℃,测温电阻与模块上3个高精度电阻组成电桥,按照电桥工作原理,桥臂电阻的阻值应小于测温电阻的最小值,并应当考虑一定的冗余,温度系数的计算公式为R0×3.85×10-3,其中R0是0℃电阻,由于采用了高精度电阻和12位的AD,A/D转换精度》0.5 ℃,可用多路开关实现。电桥两臂中点分别接入运算放大器进行跟随处理,再经后级放大后由A/D转换芯片采集温度测试结果,A/D转换芯片采用串行接口芯片,与DSP的McBSP1接口连接,该芯片分辨率为12位,并具有10 μs的转换时间及最大11路的A/D输入。

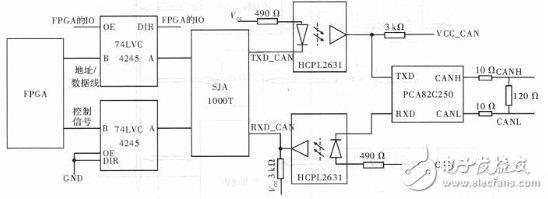

在车载导航系统电路设计中采用了CAN总线设计。CAN总线独立控制器采用SJA1000T,使用16 MHz晶振作为时钟输入,可通过软件配置ID号和数据传输波特率,最大速率为1 Mbit·s-1。其总线控制器使用数据地址复用总线,经FPGA转换后与DSPEMIF总线连接。CAN总线控制器信号采用TTL电平(5 V),与信号为3.3 V电平的FPGA之间需使用SN74LVC4245作电平转换。CAN总线接收器采用Philips Semiconductors公司PCA82C250.其总线控制器与收发器之间的数据传输信号采用光耦进行隔离。CAN总线接口电路如图2所示。

图2 CAN总线接口电路

2.4 FPGA设计

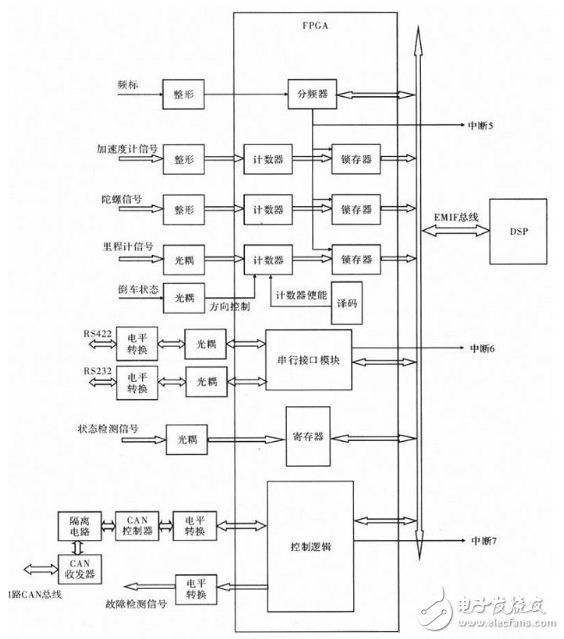

车载导航系统电路采用FPGA处理模块上控制逻辑、各输入信号的计数及实现串行接口通讯协议。FPGA对输入信号进行计数,并对标频信号分频产生中断5信号,产生中断5信号的同时对各计数器值进行锁存。DSP可通过EMIF总线访问FPGA的内部资源,地址空间占用EMIF总线的CE2.FPGA的加载模式为主控串行模式(Master Serial Mode),FPGA功能框图如图3所示。FPGA设计包括加速度计信号计数器设计、陀螺信号计数器设计、里程计信号计数器设计、陀螺合频计数器设计、标频分频器设计、状态检测、故障检测信号和串行通讯接口设计。

图3 FPGA功能框图

加速度计信号输入为可逆脉冲,每个通道加速度计输入包括3路信号,分别是+A、-A和GND,按照设计要求,+A信号上有脉冲时计数值增加,-A信号上有脉冲时计数值减少,当频标分频中断产生时,将计数结果存入锁存器内。在FPGA中设计了16位的计数器,上电复位计数器为0,+A信号上有脉冲时计数值加1,-A信号上有脉冲时计数值减1,当频标分频中断产生时,将计数结果存入锁存器内,DSP可通过EMIF访问锁存器得到加速度计信号计数器的结果。

陀螺信号输入形式为正交编码信号,每个通道陀螺信号输入包括3路信号,分别是A、B和DGND,当A相超前B相90°时计数值增加,当A相落后B相90°时计数值减少。在设计时输入信号先经过鉴相电路,识别A路和B路信号的相位先后,并产生两路4倍频的可逆脉冲信号,然后对可逆脉冲进行计数,当标频信号中断产生时,将计数结果存入锁存器内。

里程计信号包括两路计数输入和一路行车状态信号输入,计数输入每路使用一个16 bit计数器,当中断产生时将计数器数值存入锁存器;行车状态信号(STATE)上电初始为无效状态,用户通过命令设置STATE状态是否有效。其STATE信号处于有效状态时,STATE为1,里程计计数器递增计数;若STATE为0时,里程计计数器递减计数;而当STATE信号处于无效状态时,里程计计数器递增计数。

在FPGA中设计了16位计数器,上电复位计数器为0,计数器的值均增加,而计数器均加1,当频标分频中断产生时,将计数结果存入锁存器内。DSP可通过EMIF访问锁存器得到陀螺合频计数器的结果。

标频分频器用来将标频信号分频,产生锁存FPGA内加速度计数器、陀螺计数器、里程计计数器的计数值以及状态检测信号的状态中断信号。在FPGA中标频分频器由一个预定标器和一个计数器组成,可由软件编程设置分频,DSP通过EMIF总线向预定标器写入需分频的数值,计数器记录频标脉冲的个数,计

- 基于AD73360和TMS320F2812的数据采集系统设计(12-06)

- 基于紫外检测法的智能型特高压验电器系统(03-17)

- 单一DSP控制两套三相逆变器的实现(08-31)

- 基于DSP生成SVPWM在逆变电源中的应用(11-09)

- DSP的大功率开关电源的设计方案(12-01)

- DSP处理器电源方案设计(02-08)