推动串行互连革命

串行互连构成现代通信系统的关键基础,因此串行器/解串器 (SerDes) 的选择可以对系统成本和性能产生很大的影响。尽管传统的基于数据通信 的SerDes 是为适迎合面向字节(byte-oriented)、基于数据包(packet-based)的总线而设计,但许多电信应用使用其他总线格式。这使得将SerDes技术设计到这些系统中变得很困难。本文概述了 SerDes 的体系结构,并且显示说明某一个体系结构如何特别适用于电信信号处理系统。

SerDes 体系结构:概览

并联时钟 SerDes 将并行宽总线串行化为多个差分信号对,传送与数据并联的时钟。这些 SerDes 比较便宜,可以在通常需要同时使用多个 SerDes 的应用中,通过电缆或背板有效地扩展宽总线。

图 1. DS90CR217 21位通道链路(channel-link)并联时钟串行器

|

Input latch |

输入闩锁 |

|

Mux |

多路复用器 |

8b/10b SerDes 将每个数据字节映射到 10 位代码,然后将其串行化为单一信号对。10 位代码是这样定义的:为接收器时钟恢复提供足够的转换,并且保证直流平衡(发送相等数量的"1"和"0")。这些属性使 8b/10b SerDes 能够在有损耗的互连和光纤电缆上能够以较少的信号失真高速运行。

图 2. 8b/10b 串行器方框图

|

8b/10b serializer |

8b/10b 串行器 |

|

LVDS or CML |

LVDS 或 CML |

|

Input latch |

输入闩锁 |

|

8b/10b encoder |

8b/10b 编码器 |

|

Mux |

多路复用器 |

|

Value(decimal) |

值(十进制) |

|

Value(binary) |

值(二进制) |

|

10-bit code |

10 位代码 |

|

Alternate code |

可选代码 |

|

K28.5 special code |

K28.5 特殊代码 |

|

Comma |

逗号 |

位交错 SerDes 将多个输入串行流中的位汇聚为更快的串行信号对。此类型的 SerDes 以最少的布线将吞吐量最大化。

图 3. 位交错串行器方框图。

|

Bit interleave SerDes |

位交错 SerDes |

|

Input latch |

输入闩锁 |

|

Mux |

多路复用器 |

嵌入式时钟位(又称为 开始-停止)SerDes

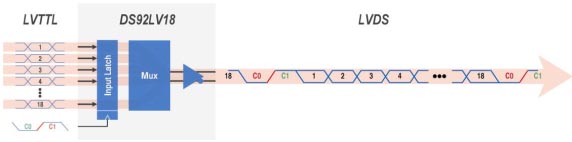

图 4. DS92LV18 18 位总线 LVDS 嵌入式时钟为串行器

|

Input latch |

输入闩锁 |

|

Mux |

多路复用器 |

可选总线宽度

嵌入式时钟位体系结构可以将数据总线和时钟串行化为一个串行信号对。两个时钟位,一低一高,在每个时钟循环中内嵌入串行数据流,对每个串行化字(word)的开始和结束成帧(因此,为可选替代的名称为"开始-结束位"SerDes),并且在串行流中创建立定期的上升边沿。由于有效负载夹在嵌入式时钟位之间,因此数据有效负载字宽度并不限定于字节的倍数。实际上,10 和 18 位总线的产品已面世。

图 5. 定期嵌入式时钟位转换。

|

Period embedded clock transiTIon |

定期嵌入式时钟位转换 |

接收器锁定到随机数据

加电之后,接收器自动搜索定期嵌入式时钟的上升边沿。由于数据有效负载的数据位会随着时间的推移而更改值,但是时钟位不随时间发生更改,因此接收器能够定位独特的时钟边沿并与其保持同步。锁定之后,接收器从串行流中恢复数据,而不管有效负载数据模式如何。这种自动同步功能通常称为"锁定到随机数据",并且无需外部系统干预。在接收器位于不受系统直接控制的远程模块的系统中,以及其中一个发送器广播至多个接收器的系统中,这是一种特别有用的功能。在广播情况下,插入总线的新接收器模块将锁定到随机数据,无需通过发送培训模式或字符来中断到其他接收器的通信

- LT3751如何使高压电容器充电变得简单(08-12)

- 三路输出LED驱动器可驱动共阳极LED串(08-17)

- 浪涌抑制器IC简化了危险环境中电子设备的本质安全势垒设计(08-19)

- 严酷的汽车环境要求高性能电源转换(08-17)

- 适用于工业能源采集的技术 (08-10)

- 单片式电池充电器简化太阳能供电设计(08-20)