推动串行互连革命

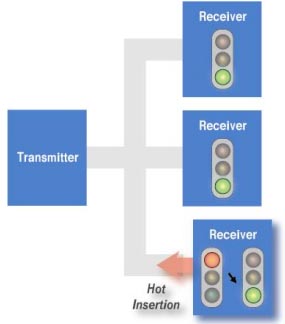

加电之后,接收器自动搜索定期嵌入式时钟的上升边沿。由于数据有效负载的数据位会随着时间的推移而更改值,但是时钟位不随时间发生更改,因此接收器能够定位独特的时钟边沿并与其保持同步。锁定之后,接收器从串行流中恢复数据,而不管有效负载数据模式如何。这种自动同步功能通常称为"锁定到随机数据",并且无需外部系统干预。在接收器位于不受系统直接控制的远程模块的系统中,以及其中一个发送器广播至多个接收器的系统中,这是一种特别有用的功能。在广播情况下,插入总线的新接收器模块将锁定到随机数据,无需通过发送培训模式或字符来中断到其他接收器的通信。

图 6. 在热插入期间接收器自动锁定到随机数据。

|

Transmitter |

发送器 |

|

Receiver |

接收器 |

|

Hot inserTIon |

热插入 |

宽松的时钟要求

大多数 SerDes 依靠严格控制发送和接收时钟的抖动来实现锁定和锁定监测。然而,嵌入式时钟位接收器对输入的嵌入式时钟上升边沿进行同步,并且仅在初始同步期间才需要接收器参考时钟,以防止锁定至假谐波。这可以将发送和参考时钟的抖动要求宽松至少一个数量级。实际上,接收器参考时钟只需在发送时钟频率的 ± 50,000 PPM的范围内即可。这在使用非标准振荡器的系统中可以节省大量成本,因为可以使用成本非常低的标准频率。

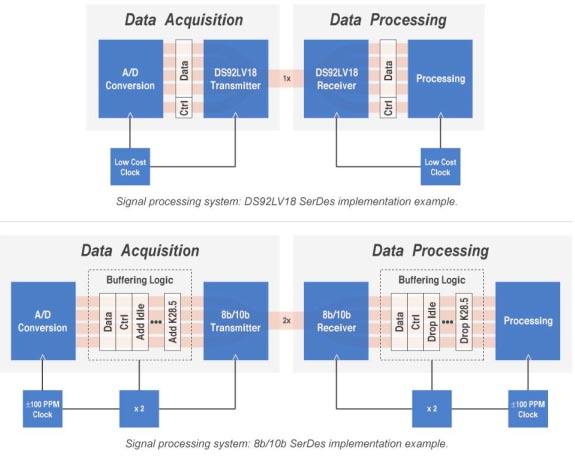

系统比较

嵌入式时钟位 SerDes 特别适用于发送原始数据以及控制、奇偶校验、帧、状态等其他信号的应用。例如,基站、汽车影像/视频和传感器的信号处理系统,这里模拟/数字转换器、相机或显示器将原始数据传递给链路另一端的信号处理单元。为进行说明,假定在图 7 的数据采集系统中使用美国国家半导体公司的 DS92LV18。这里DS92LV18 不仅将数据串行化,而且也将两位附加信息串行化,例如,奇偶校验、状态位等。这些位与数据位一起以正常的A/D 采样速率进行串行化,这样便无需使用数据缓冲或附加逻辑电路。

图 7.基于 DS92LV18 SerDes(上面)和 8b/10b SerDes(下面)实现的信号处理系统示例实现。

|

Data acquisiTIon |

数据采集 |

|

A/D conversion |

A/D 转换 |

|

Data |

数据 |

|

Ctrl |

控制 |

|

Transmitter |

发送器 |

|

Low cost clock |

低成本时钟 |

|

Data processing |

数据处理 |

|

processing |

处理 |

|

Signal processing system: DS92LV18 SerDes implemenTIon example. |

信号处理系统:DS92LV18 SerDes 实现示例。 |

|

Buffering logic |

缓冲逻辑 |

|

Add idle |

添加空闲 |

|

Drop idle |

丢弃空闲 |

|

Signal processing system: 8b/10b SerDes implemention example. |

信号处理系统:8b/10b SerDes 实现示例。 |

在同一个应用中使用 8b/10b SerDes 将更加复杂。附加的非面向字节控制信息必须以字节格式缓冲和发送。K28.5 逗号字符还必须在开始链路同步时发送,这就需要附加逻辑电路。这些附加的"非数据"字节需要 SerDes 比数据转换速率更快地操作。这不仅对背板或电缆设计提出了更高的要求,而且需要某种空闲插入/删除流控机制。尽管在数据通信系统中通常已经存在此类缓冲,但在许多非数据通信应用中,这种附加数据处理增加了不必要的开销和复杂性。本示例说明若干附加位如何对系统设计产生重大影响。

结论

如今的设计人员不必再必须使应用适应 SerDes,反过来可以根据应用选择合适的 SerDes。嵌入式时钟位 SerDes正在逐渐普及流行, 它增加了设计的灵活性,可以大幅减少系统成本和复杂性。

- LT3751如何使高压电容器充电变得简单(08-12)

- 三路输出LED驱动器可驱动共阳极LED串(08-17)

- 浪涌抑制器IC简化了危险环境中电子设备的本质安全势垒设计(08-19)

- 严酷的汽车环境要求高性能电源转换(08-17)

- 适用于工业能源采集的技术 (08-10)

- 单片式电池充电器简化太阳能供电设计(08-20)