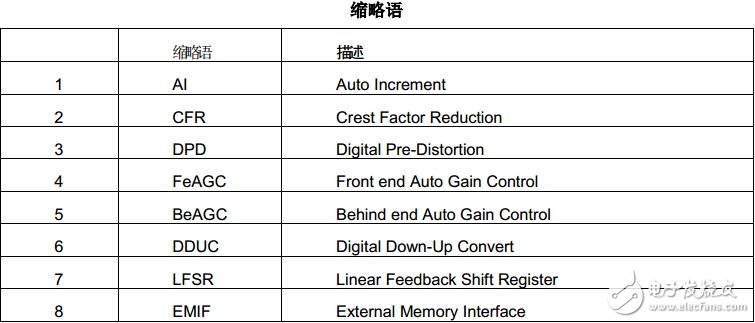

TI数字中频芯片GC6016配置与应用分析

摘要

GC6016 是 TI针对数字直放站应用而推出的一款数字中频处理芯片。本文主要描述了 GC6016 的加载流程,初始化配置,数据采集配置,以及和上下游芯片的配合调试方法。

1、 概述

GC6016是TI针对数字直放站应用而推出的一款数字中频处理芯片。与其同时推出的类似芯片还有GC5330。其中GC6016除了CFR和DPD外,具有GC5330的所有功能,包括DUC, TX

equalizer, Bulk Up converter, RX equalizer, DDC, feAGC,beAGC, I/Q imbalance correcTIon, DC offset cancellaTIon. 其处理能力达到48个上下行通道,最大支持4个发射天线或者8个接收天线,支持灵活的小数倍率重采样配置,支持多模配置。能够很好的应用于各种 3GPP,3GPP2以及 MC-GSM等无线标准。

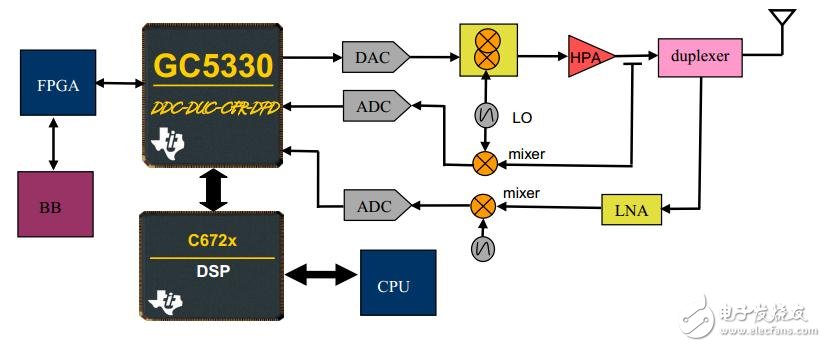

GC5330的应用结构如下图所示。图中可以看到,GC5330需要DSP配合才能实现完整功能。事实上,DSP不但完成DPD的算法处理,还完成芯片加载与配置功能。这些功能均通过 DSP向主控 CPU提供的 API函数实现。

图 1. GC5330应用结构图

GC6016的应用架构如下图所示。从图中可以看出,GC6016无需外挂 DSP,其不能支持DPD。CPU通过EMIF或者 SPI直接访问 GC6016芯片。因此其所有配置与控制都需要在 CPU直接实现。因此配置流程以及芯片控制都需要用户编程实现。

图 2. GC6016应用架构图

本文的目的在于帮助用户快速高效的配置与控制GC6016.

2、 GC6016功能介绍

GC6016支持目前主流的基站收发信机标准,包括:3GPP(LTE、WCDMA、TDSCDMA)、

3GPP2(CDMA2000)、MC-GSM、wimax 以及WiBRO(OFDMA)。

GC6016支持混模,典型混模型态比如 LTE+WCDMA,LTE+TDSCDMA。

GC6016支持最大48个载波处理,支持小数倍抽取、插值;

芯片最大速率支持 368M;

支持最大4路发射天线,8路接收天线;

支持接收FeAGC,BeAGC;

支持数据采集;

外部接口支持SPI(3 or 4 wire)或者 EMIF;

支持各节点增益调整,功率统计;

支持收发均衡;

与基带FPGA、AD及DA之间支持多种速率和格式接口;

23x23mm,484-ball TE-PBGA封装;

GC6016的功能框图如下所示。

图 3. GC6016功能框图

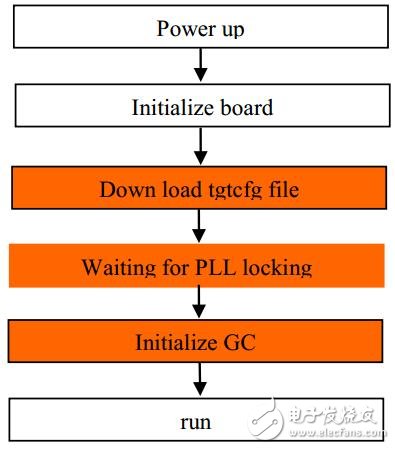

3、 GC6016的上电配置流程

GC5330/6016的配置文件是扩展名为tgtcfg的文本文件,包含了GC运行以及业务支撑的全部信息。由于该芯片支持多种通讯标准,并且可以按照客户需要灵活配置,因此针对不同的系统需求,该tgtcfg文件不同。该文件由TI根据客户需求产生并提供给客户。

系统上电之后,应该首先配置好单板,包括 CPU自身、电源、FPGA、时钟、AD以及 DA等芯片(需要说明的是,一般需要等到系统全部配置完成之后才会打开发射同道)。

然后下载GC配置文件。配置文件一般会有超过 60000次的寄存器写操作。如果使用 50M速率EMIF接口,耗时大概在几十毫秒;如果采用 SPI接口,则耗时会增大,这一点系统设计时需要考虑。

配置下载完成之后,进入等待 PLL锁定状态。在该状态下需要判断寄存器 0是否为1,为 1表示复位成功。必须该状态有效才可启动下一步操作。

GC初始化状态完成芯片使能。需要说明的是,GC的初始化需要用到外部的同步信号 syncA,该信号一般由FPGA提供,用于使能芯片配置寄存器,该 syncA信号也用于数据采集或者对芯片在线配置的使能。关于芯片初始化,TI提供相应的样例供参考。典型情况下syncA信号的周期是5ms或者 10ms,脉宽是8个 BB时钟周期,该信号在时序上需要和 BB_frame信号上升沿对齐。

图 4. GC6016初始化流程图

4、 GC6016的增益调整

GC6016提供各个节点的增益调节功能。

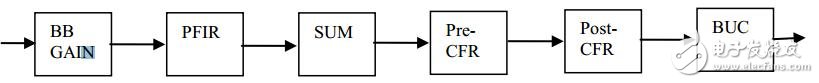

下行通道可调整增益的节点如下图。对于发射通道,大部分情况下,调整 BB gain,sum gain, pre-CFR以及 post-CFR 4个节点就可满足客户需求。对于其他节点,如非必要,不建议调整。

图 5. GC6016下行增益调节节点

上行通道可调整增益的节点如下图。

图 6. GC6016上行增益调节节点

各模块的增益调节范围及精度如下表所示。其中,BB_gain节点需要通过读写AI寄存器修改并同步,pre-CFR及 post-CFR节点修改后需要同步。

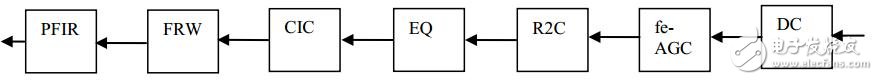

另外请注意,除了BBgain,pre_cfr_gain和post_cfr_gain可以精确调整增益外,其他几个节点只支持 6dB步进调整。R2C为实数到复数的转换,如果使能该模块,则固定增益为-3dB。feAGC也可配置为固定增益模式,其增益精度和范围由增益表以及配置确定。对于 PFIR,也可以通过修改系数调整增益。

Table 1. 表 1. GC6016内部增益

5、 GC6016 capture buffe

- 德州仪器:将主动安全升级为标准配置(02-21)

- 基于DSP和FPGA的机器视觉系统设计与实现(03-07)

- 剖析智能手表内部芯片硬件结构:哪些厂商获益?(03-21)

- 加快TPA2028D1对突发音信号(短暂提示音)的响应(04-10)

- 德州仪器ZigBee单芯片推动物联网应用(05-17)

- 3G/4G时代数据暴增 TI小基站基带芯片轻松应战(07-23)