开放式FPGA增加测试灵活性

的中心频率和功率电平进行调整。在调整过程中可以遵循以下步骤:

●根据待测设备的估算增益,选择一个起始VSG功率电平。

●设置VSG功率电平。

●等待VSG稳定。

●等待DUT稳定。

●使用功率计进行测量。

●如果功率在量程内,则退出。否则计算新的VSG功率电平,并返回步骤2.

调整所需的时间取决于待测设备的类型、所需的精度以及所使用的仪器类型,通常为几百毫秒到几秒。调整完成后,使用VSA进行性能测量。

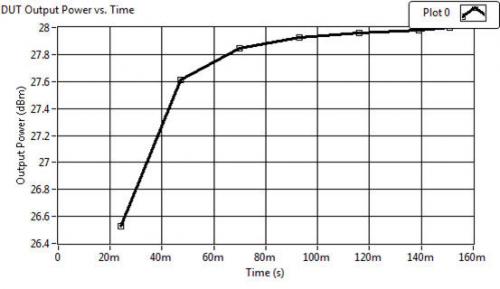

图4显示的是一个待测设备在调整过程中的输出,该设备采用传统方法来获得28dBm的平均输出功率。如果功率放大器的增益呈线性且匹配数据表中规定的标准增益,则VSG生成的第一个点会输出28dBm的功率。相反,放大器的输出只有26.5dBm,这说明功率放大器规定的标准增益并不准确。因此,需要对VSG输出功率进行调整,同时VSA捕获另一个点。此时的平均功率为27.6dBm,这表明了放大器处于增益压缩状态。总体上,该方法需要七个步骤以及大约150毫秒的时间才能使放大器的输出达到所需的级别。在这个例子中,每个步骤的待测设备稳定时间为10ms.但是,稳定时间根据每个待测设备而有所不同,这会大大影响整体的调整时间。

图4.调整功率放大器输出的传统方法显示了功率电平呈逐步增大状态。

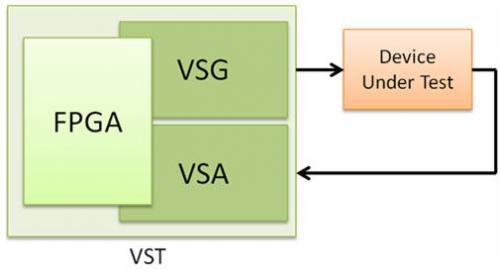

VST(矢量信号收发仪)结合了VSG、VSA和FPGA.这一组合使您可将功率调整算法的运行转移到硬件上。在图5中,虽然没有功率计,但是您也可以运行一个系统校准步骤,在VSA上获得与功率计相同的精确度。

图5.矢量信号收发仪结合了信号发生器、信号分析仪和FPGA.

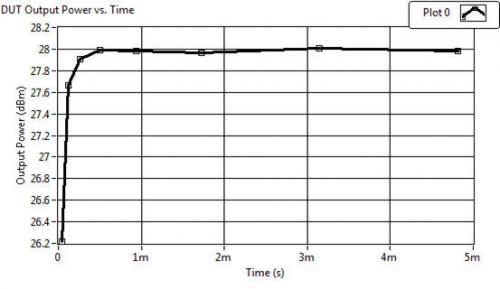

功率放大器的输出功率调整步骤类似于传统方法步骤,不同的是调整循环是在开放式FPGA内部运行。在FPGA内运行循环可大大降低每次调整所需的时间。与在主机上运行控制循环相比,通过使用开放式FPGA,并在FPGA上执行控制循环,调整待测设备输出功率所需的时间将大大缩短。对于本例中的DUT,功率调整只需大约5毫秒,而采用传统方法则需要150毫秒。请注意,基于硬件的方法比传统方法多一个步骤。但是,调整所需的总体时间却少得多。与图4相比,在图6中,前面几个步骤执行的速度非常快(缩短了平均时间),之后随着调整循环的收敛,点之间的间距不断增大。

图6.与传统方法相比,基于硬件的调整可使功率电平上升的时间大大缩短。

信号处理

用户可编程FPGA最典型的应用之一是减少仪器上必须发送回主机进行处理的数据量,从而将通信总线释放出来进行其他数据传输,同时降低了CPU的负荷。常见的方法包括对采集的数据集进行复杂触发、滤波、峰值检测或者执行FFT(快速傅立叶变换)。

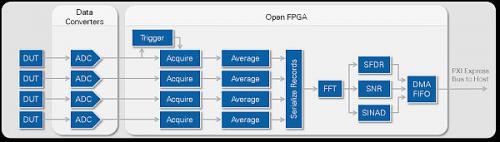

例如,在图7所示的应用中,有四个待测设备需要并行进行测试。ADC(模拟数字转换器)将采样数据传送至FPGA,但当收到一个自定义触发才会开始采集数据。在采集数据时,FPGA会对测量结果进行实时平均,然后将计算结果序列化到记录中。接着,对记录的数据进行FFT,然后开始测量SFDR(无杂散动态范围)、SNR(信噪比)和SINAD(信噪失真比)。这些结果仅仅是来自ADC的输入信号的一小部分数据,通过DMA FIFO(直接内存存取,先入先出)机制传输至主机。

图7.开放式FPGA可让您采集数据、对信号取平均值以去噪、将并行数据转化为串行数据,并应用数学运算、FFT和滤波。

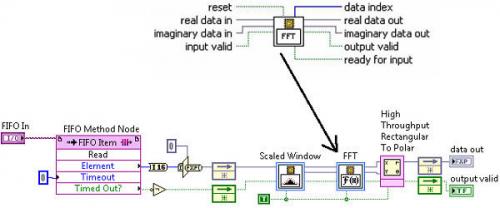

FFT作为DSP中的一个基本函数,FFT可用于许多测试应用。FPGA具有这个功能有助于测试频域触发、数据压缩、基于频率的闭环控制和图像处理等应用。图8显示了该示例如何使用LabVIEW FPGA实现FFT.

图8.代码显示了开放式FPGA上执行FFT的位置。

虽然本文提到的仅仅是FPGA几个令人激动的数字信号处理功能,但是FPGA上还具有许多其他功能可用于测试应用中。许多开放式FPGA均具有这种处理功能,图9显示的是NI硬件通过LabVIEW FPGA可实现的一些处理类型。

图9. FPGA上具有的数字信号处理功能包括数学运算、滤波、三角函数和视频处理。

随着开放式FPGA在整个测试测量行业的日益普及,具有固定功能的仪器将会逐步被淘汰。相反,仪器的功能将越来越多地由软件来定义,这类似于"应用程序"为移动设备行业带来的变革。测试应用程序将不再受限于测试厂商可以开发何种软件功能,而是受限于硬件和使用该仪器的工程师的想象力。

- 用数字荧光示波器对开关电源功率损耗进行精确分析(11-04)

- 数字荧光示波器结构融合模拟示波器和数字示波器的优势(03-03)

- 秘密武器助你从容应对噪声检测难题(03-29)

- 使用采样示波器对PCB进行串扰分析(11-06)

- 具有可调触发灵敏度的示波器可有效提高电路检测质量(01-11)

- 在手持式示波表上捕捉间歇性信号(01-25)