多遥测天线集中校准源的设计与应用

,说明m序列发生器的在FPGA中的设计及具体测试环节。

9级m序列的本原多项式为x9+x4+1,为了配合接收机,这里使用了9级m序列本原多项式的逆多项式x9+x5+1.该m序列发生器可产生周期为29-1=511的最长序列。

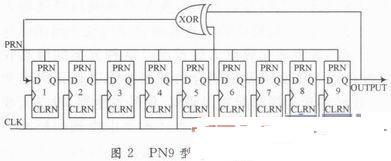

图2是9级m序列在FPGA中的实现电路。设计中使用了9个DFF(D触发器)前后级联,第5级和第9级的输出经过一个异或门后反馈给最前级的DFF.通过各个DFF的预制端来设置其初始状态,由于移位寄存器进入全"0"状态后输出全为"0",因此在预置时避免其初始状态为全"0"。为测试方便,这里将各个触发器的预制端上电后置"1"。

图3为位速率10 Mb/s的9级m序列在Altera公司的QuartusⅡ软件中的仿真波形,生成的m序列通过与状态转移得出的m序列码元对比,两组码元完全一致。可得出本方案的可行性。

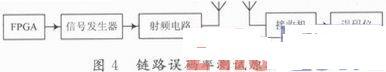

在实际应用中,将FPGA的m序列输出管脚接至信号发生器的信号输入端,m序列码元在信号发生器中经过FM调制由射频电路中的天线发送出去。接收端的天线将接收的FM信号送入遥测接收机,在接收机中经过解调和位同步后,将数据和接收机中锁相环锁定的时钟同时接至误码测试仪,在误码测试仪中读出误码率,以测定整个链路的误码率,或者通过接收机中的误码测试程序读出误码率。图4给出了误码率测试原理图。

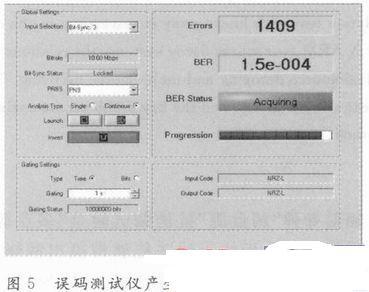

图5为误码测试仪产生m序列在IN-SNEC公司接收机中自带的误码率测试程序的截图。在试验中,使用了9级m序列作为误码率测试的m序列,位速率为10 Mb/s.可以看出,链路状态良好,位同步良好,误码率为1.5×10-4.

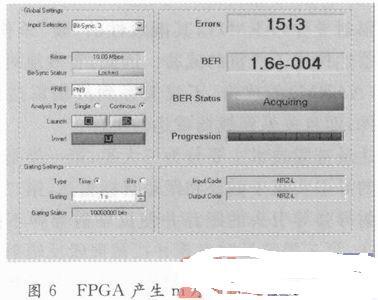

图6为FPGA产生m序列在IN-SNEC公司接收机中自带的误码率测试程序的截图。同样使用9级m序列作为误码率测试的m序列,位速率为10Mb/s.从图中可以看出在链路状态一致的情况下,FPGA中m序列发生器可以替代误码测试仪。

在同一链路状态下,对不同速率下的同一m序列及同一速率下的不同m序列进行了测试。测试结果均与误码测试仪测误码率几乎一致。

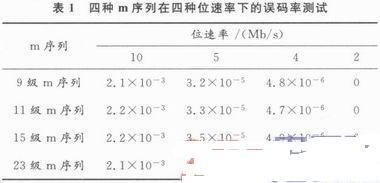

表1为四种m序列在四种位速率下的误码率测试结果。

从上述的测试中可以看出,FPGA中m序列发生器可完全替代误码测试仪进行遥测链路的误码率测试。

3方案的不足和改进

由于遥测技术逐渐向网络化发展,新型测试设备均支持远程控制,网络的引入不仅优化了整个遥测链路,同时大大节约了人力成本。实际使用中用于测试误码率的伪随机序列发生器置于接收机的远端,需要专人值守,人们希望通过网络远程控制伪随机序列发生器,因此误码测试仪不支持网络控制的弊端就显现出来。针对这种状况,在进一步的m序列发生器的研制中,本文提出了一种支持网络远程控制的遥测链路误码率测试方案:使用可网络控制的FPGA产生m序列进行整个通信链路的误码率测试继而完成遥测天线的校准工作。

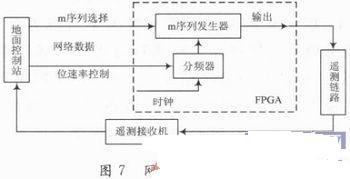

图7为网络控制示意图。操作员通过地面控制站中的微机发送网络控制信号(主要包括四种m序列的选择信号和四种典型位速率的控制数据)给FPGA,FPGA识别控制信号后输出特定位速率的特定m序列用于校准使用。

4结论

本文讨论了利用线性反馈移位寄存器结构在FPGA内部简捷、高效地实现m序列发生器的方法。提出了通过网络控制端口,利用微机远程控制FPGA中m序列的码型和进行速率控制,从而实现遥测链路测试的网络化。并将生成的伪随机码用于遥测天线的校准(利用FPGA产生的m序列测试遥测链路的误码率)。从测试可以看出,FPGA中产生的m序列码型正确无误,可以进行多种码型多种速率的误码测试。与传统误码测试相比,本方案具有体积小,功耗小,易于实现等特点,充分发挥了线性反馈移位寄存器结构简单,速度快的特点。

...........................................................

与非深度解读系列:

半导体公司"大学计划"的追问和真相

大环境的不景气是就业环境恶化的元凶,但是也让我们不禁追问半导体公司的大学计划对于学子们的真正意义。厂商们的大学计划都在做些什么?那么多的联合实验室有得到充分利用吗?大学计划的直接体验者--老师和学生们是否真正从中受益…….【专栏作者:高扬】

本土IC公司调查笔记

全球经济不景气的大环境下一些本土IC公司的创新能力、管理能力、抗风险能力、盈利能力,甚至公司创立的动机都受到一些质疑。一方面官方的消息总是告诉我们中国的半导体产业得到了长足的进步;而街巷小道中又不绝流传多少本土IC公司倒闭,多少公司靠欺骗,根本没有核心竞争力….真相只有一个,也许会随《本土IC公司调查笔记》慢慢开启…【专栏作者:岳浩】

电子屌丝的技术人生系列

在这个系列里,每个

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)