宽带阻抗测量仪的设计——微处理器电路设计

与多组总线形式的哈佛结构相关,在TMS320F2812处理器中采用了流水线操作以减少指令执行时间,允许DSP同时进行程序指令和存储数据的访问,从而增强了处理器的处理能力。在TMS320F2812中采用了八级逻辑流水线,也就是说,处理器可以并行处理多条指令,每条指令处于流水线上的不同阶段,从而实现了一种并行处理的机制。同时,TMS320F2812还具有专门针对片上Flash存储器的Flash流水线模式,能显著提高指令从Flash中执行的速度。

TMS320F2812具有低功耗的特点,它采用静态CMOS工艺,芯片供电电压为1.8V(内核)、3.3V(I/O),相比于采用5V工作电压的系统,它的功耗可降低很多。

TMS320F2812片内有多种形式的存储器及多个不同的存储空间。采用程序与数据存储器统一编址的存储体组织形式,为用户分配存储器提供了很大的灵活性。TMS320F2812提供了外部存储器接口,可扩展1M的外部存储器。由于TMS320F2812本身具有非常大的Flash,所以一般不必外扩ROM,外部RAM可以根据需要进行扩充。

TMS320F2812片上外设资源也非常丰富,有两个事件管理器模块EVA和EVB,可以处理与时间有关的时间事件和外部中断事件,每个事件管理器都包括2个16位的通用定时器、8个16位PWM输出通道、3个全比较单元、3个外部事件捕获单元、1个正交编码脉冲单元。

TMS320F2812还具有3个独立的CPU定时器、局域网CAN2.0B总线控制器、16通道的12位ADC(最小转换时间为60ns)、两个串行通信接口(SCI,Serial Communication Interface),一个16位串行外设接口(SPI,Serial Peripheral Interface),多通道缓冲串行接口(McBSP,Multi-channel Buffered Serial Port)以及看门狗时钟单元。

TMS320F2812具有多个可变工作频率,可以使CPU工作在较高频率上(最高工作频率是150MHz),而其它功能模块如定时器、SCI模块、A/D转换器等以及外围模块可工作在同一较低频率上。

另外,TMS320F2812还拥有56个复用的独立可编程的通用I/O口,分为6个端口,另一方面,TMS320F2812具有一个专门的外设中断扩展块,可支持45个不同的外设中断。

5.2 DSP最小系统电路

以TMS320F2812 DSP为核心的DSP最小系统除了DSP芯片部分还包括:时钟电路;监控电路;JTAG仿真接口;电源管理电路;外部扩展存储器等五部分,具体电路如图5-1所示。

5.2.1时钟电路TMS320F2812有多个部件需要时钟,有CPU、看门狗电路、ADC和事件管理器等片上外设。

5.2.1.1 CPU时钟

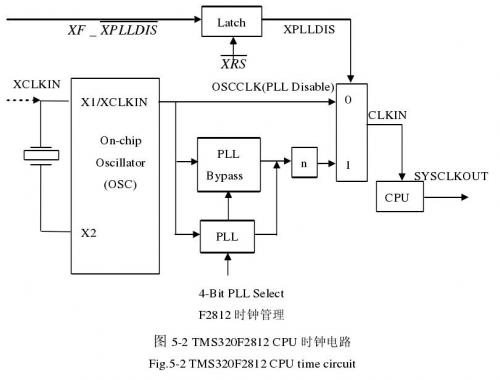

F2812的CPU时钟电路如图5-2所示。

F2812DSP的时钟发生器允许设计者选择时钟源:一是在X1和X2之间接一晶振来启动内部晶振,EXTCLK接地。二是将外部时钟直接接到X1管脚,X2悬空,XIN接地。

设计中用30MHz外部晶体给F2812提供时钟,并使能F2812片上PLL电路。

PLL倍频系数由PLL控制寄存器的低4位控制,可由软件动态修改,外部复位信号(XRS)将此4位控制位被清为0,F2812的CPU最高可工作在150MHz主频下,也即对30MHz输入频率进行5倍频。

5.2.1.2片上外设时钟需要时钟信号的片上外设有:看门狗电路WatchDog,CPU定时器、eCAN总线控制器;SCI、SPI、MCBSP;EV、ADC。

片上外设按输入时钟分为4个组:

1.SYSOUTCLK组:CPU定时器、eCAN总线;

2.OSCCLK组:看门狗电路;

3.低速组:SCI、SPI、MCBSP,它们的输入时钟信号由SYSCLKOUT经低速外设分频器分频得到;

4。高速组:EVA/B、ADC,它们的输入时钟信号由SYSCLKOUT经高速外设分频器分频得到。

与PLL、时钟配置相关的寄存器有:

1.PLLCR:用于设置PLL倍频系数;

2.HISPCP:用于设置HSPCLK的分频系数;

3.LOSPCP:用于设置LSPCLK的分频系数;

4.PCLKCR:用于对高速、低速片上外设的运行进行启/停控制。

各外设时钟都可由对相关寄存器编程来实现。

5.2.2电源管理电路

TMS320F2812的工作电压分为两组,一组是供CPU内核使用的1.8V的VCCCORE,设计上选用TI公司的TPS76718电源管理芯片,将+5V的电压变换为+1.8V;另一组是供I/O口使用的3.3V的VCCIO,选用TI公司的TPS76733电源管理芯片将+5V电压变为+3.3V。电源管理电路图如图5-3所示。

在设计DSP芯片与其它外围芯片的接口时,如果外围芯片的工作电压也是3.3V,那么就可以直接连接。但是现在许多外围芯片的工作电压都是5V,为了使3.3V芯片与这些5V供电芯片可靠接口,应根据各种电平的转换标准来设计。

当电平转换标准不一致或者由于承受电压的限制而不能直接相接时,需要在两者之间增加一个缓冲器件。本论文选用TI公司的74ALVC164245作为缓冲器件来设计两者的接口。它采用3.3V和5V双电压供电。

除上述电路说明外,其它连接主要有:对一些未使用的输入引脚接10k或20k上拉电阻或下拉电阻使其电平状态稳定;对要进行功能切换的引脚加跳线以备选择。

5.2.3外部扩展存储器

宽带阻抗测量仪 微处理器 DSP TMS320F2812 相关文章:

- 宽带阻抗测量仪的设计——信号发生电路设计(01-09)

- 宽带阻抗测量仪的设计——信号发生电路设计 (三)(01-17)

- 宽带阻抗测量仪的设计——信号检测电路设计(01-18)

- 宽带阻抗测量仪的设计——信号发生电路设计 (二)(02-06)

- 宽带阻抗测量仪的设计——信号检测电路设计(二)(02-06)

- 宽带阻抗测量仪的设计——阻抗测量理论及其方法(01-16)