宽带阻抗测量仪的设计——信号发生电路设计 (二)

2.2信号发生电路

2.2.1时钟信号发生器电路

由于AD9858内部没有时钟发生电路,所以需要外部时钟源提供时钟信号,本系统采用NBC12439为AD9858提供时钟信号,NBC12439内部是一个带有压控振荡器(VCO)的锁相环电路,它的参考频率可以是外加时钟或者由内部振荡电路产生(这时外加晶振频率在10~20MHz之间),由于内部锁相环具有可变分频比功能,因此NBC12439是可以数字控制的时钟发生器芯片,可以产生高达800MHz的正弦波,具有并行和串行两种接口,本系统采用并行口来进行控制。其控制简单,实现容易。其输出信号频率稳定度和精度与外加晶振的频率稳定度和精度相同。一般晶振的频率稳定度和精度都很高,能够满足系统的要求。

2.2.2 AD9858设置

在信号发生电路中,AD9858工作在扫频模式下产生所要求的信号。为使其产生所需的信号,必须对它进行适当的设置。

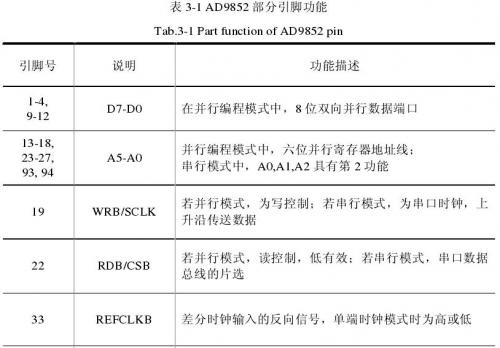

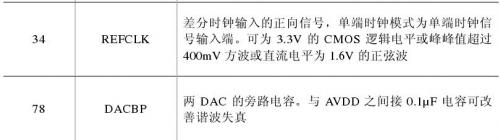

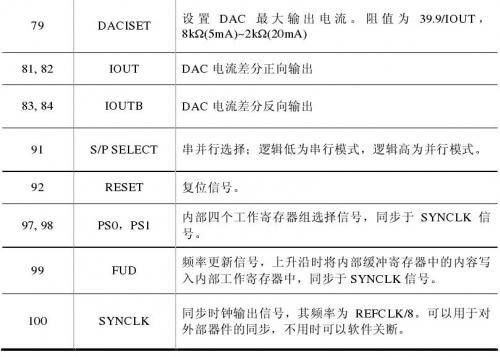

AD9858的部分引脚的功能说明如表3-1。

在本系统中,AD9858通过并行端口对内部寄存器进行控制;采用差分时钟输入;DAC输出电流最大为40mA。按照表3-1中相关的引脚功能说明,在实际的硬件电路中做如下设置:引脚91(S/P SELECT)接高电平(3.3V),则选择对AD9858采用并行方式进行数据交换;引脚79(DACIST)接3.9K电阻到地,则设定了DAC输出电流的最大值20mA;PS0,PS1接DSP的地址线,可以对内部四个工作组寄存器进行快速选择,从而实现快速频率转换。

FUD引脚接到DSP上,通过它将DDS内部寄存器中的内容写入DDS内核,从而实现相应功能。

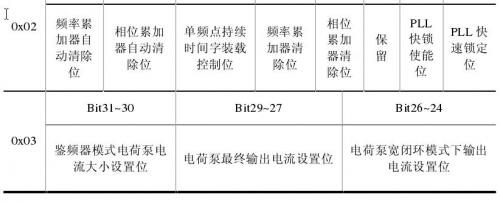

AD9858内部具有两大类寄存器:数据寄存器和控制寄存器。数据寄存器分为:频率增量改变字寄存器、单频点持续时间寄存器、四个频率改变字寄存器(0~3)、四个相位偏移字寄存器(0~3)等;控制寄存器分为4个8位寄存器,主要完成AD9858的各部分功能的控制,其控制功能分别是:节能控制、时钟控制、旁路控制、锁相环分频比控制、锁相环工作模式控制、电荷泵电流大小控制、DAC输出正/余弦控制等,各寄存器的具体控制位的意义如表3-2所示。

Bit1和Bit0这两位仅用于数据线串行工作时,当Bit0为0时,MSB(高位)先传送,当为1时LSB(低位)先传送;Bit1为0时,SDIO脚配置成双向工作模式,当为1时,SDIO脚配置成输入模式。本系统中不用这二位,取默认值0。

Bit4~2这三位分别控制AD9858内部模拟混频器模块、鉴相器和电荷泵模块、DDS内核和DAC模块是否工作;为0时使相应模块处于工作状态,当为1时,分别关断相应模块。这里只让内核和DAC模块工作。取110值。

Bit5位使能SYNCLK是否输出,当为0时,SYNCLK输出,为1时关断输出。这里取值为1,不输出SYNCLK。

Bit6位控制是否2分频参考时钟信号,当为0时,对参考时钟进行2分频,为1时,不分频,这里取值为1,不对参考时钟分频。

Bit7为保留位,所以该地址控制字可以写为58H。也可以使内核和DAC模块不工作,使AD9858处于休眠方式,这时向该地址写入5CH。

Bit9~8是鉴相器反馈输入电流比设置位,00时不分频,01时2分频,1x时4分频。本系统中不用。

Bit10是电荷泵极性选择位,当为0时,适用于以地为参考的VCO。为1时,适用于以电源为参考的VCO。本系统中不用,取默认值0。

Bit12~11鉴相器参考输入频率分频比设置位,其取值方式与Bit9~8相同,本系统不用,取默认值00。

Bit13电荷泵电流偏移设置位,当为0时,电荷泵工作在正常模式,当为1时,电荷泵工作在电流偏移模式下。本系统中不用,取为默认值0。

Bit14该位为DAC输出时正或余弦选择控制位,为0时,DAC输出为余弦波形,为1时,输出为正弦波形。

Bit15为扫频控制位,为0时,AD9858工作于单音模式,为1时工作于扫频模式。该地址控制字取值根据实际需要取值有所不同,单音模式时取值:80H,扫频模式时取值:00H。

Bit16,该位的功能是使能PLL是否使用频率改变字来参与PLL快速锁定的过程,为1时,PLL快速锁定程序在锁定过程中不使用频率改变字;为0时,在锁定过程中使用频率改变字。

Bit17是PLL快速锁定使能位,为0时,快速锁定被禁止,为1时,PLL快速锁定被激活。

Bit18是保留位。

Bit19相位累加器清除位,为1时,相位累加器被同步清除,并保持清除状态直到该位变为0时。

Bit20频率累加器清除位,为1时,频率累加器被同步清除,并保持清除状态直到该位变为0时。

Bit21是单频点持续时间字装载控制位,当该位为1时,单频点持续时间字被装载进内部减法计数器时,受FUD信号触发;为0时,当计数器计到零时自动装载,怱视FUD信号。

Bit22相位累加器自动清除位,当该位为1时,在FUD信号的触发下,自动清除相位累加器;当为0时,把新的频率改变字累加到相位累加器的当前值上。

Bit23频率累加器自动清除位,当该位为1时,在FUD信号的触发下,自动清除频率累加器;当为0时,把新的频率增量改变字累加到频率累加器的当前值上。

Bit26~24电荷泵宽闭环模式下输出电流设置位,当电荷泵工作在宽闭环模式下时,电荷泵输出电流的大小由这三位决定。参见表3-3。

- 宽带阻抗测量仪的设计——信号发生电路设计(01-09)

- 宽带阻抗测量仪的设计——信号发生电路设计 (三)(01-17)

- 宽带阻抗测量仪的设计——信号检测电路设计(01-18)

- 宽带阻抗测量仪的设计——微处理器电路设计(01-20)

- 宽带阻抗测量仪的设计——信号检测电路设计(二)(02-06)

- 宽带阻抗测量仪的设计——阻抗测量理论及其方法(01-16)