基于FPGA的原型能为您做些什么

话子系统。这些应用中的每一个都不能直接访问SoC硬件,而且实际上在某种程度上违背了所有硬件考虑事项。这些应用依赖运行在协议栈较低层的软件代表自己与SoC硬件及系统其他部分通信。

我们可以归纳为:在协议栈的每一层,软件开发人员只需要一个足够准确的模型来让自己的代码认为自己运行在目标 SoC上即可。超过必要的准确度只会让模型在模拟器上的运行速度下降。实际上,任何层面的SoC建模,都要求我们把硬件和协议栈描述为比当前层面更低的一层,以便进行验证。而且在理想的情况下,我们应该只要求够用的准确度,以实现最高性能。

这种只为软件层提供"够用的准确度"的建模方法为不同的软件开发人员提供了多种不同的建模环境,供他们在SoC项目的不同阶段使用。可以采用SystemC这样的语言进行事务处理层面的建模,创建出一个准确度低但速度足够快的仿真器模型,用来同时运行许多应用。如果实时的真实数据的处理不是很重要,那么考虑采用虚拟原型方法比较好。

不过,必须完整运行整个软件协议栈或处理真实环境中的数据时,最适合采用基于FPGA的原型方法。

使用原型验证软件的实例

只有采用基于FPGA的原型方法才能够打破建模方法中准确度与性能之间内在的相互牵制关系。采用FPGA,我们既能实现实时的速度,又能以完全的RTL周期精度建模。这样,单个原型不仅能供低层软件验证要求的准确模型使用,又能供高层应用开发人员需要的高速模型使用。实际上,整个SoC软件协议栈都可以在单个基于FPGA的原型上建模。德克萨斯州奥斯汀市Freescale Semiconductor公司移动产品部的Scott Constable及其团队开展的项目就是采用FPGA验证软件的一个很好的例子。

Freescale非常想加快SoC开发进程,因为手机市场上产品生命周期短,需要产品尽快打入市场。这不仅是为了赢得竞争,也是为了避免迅速过时。通过分析流程中耗时最多的环节,Freescale发现通过加快手机3G协议测试工作可以带来最明显的效果。如果测试工作能够在流片前完成,Freescale就可以将项目时间缩短数月。与通常只有一到两年的产品生命周期而言,这非常重要。

协议测试是一个复杂的过程,就算以较高的实时速度进行,也需要一天才能完成。采用FPGA是因为这是实现必要的时钟速度,及时完成测试的唯一途径。

协议测试需要开发产品的各种软件特性,包括硬件驱动程序、操作系统和协议栈代码。虽然如前所述主要的目的是协议测试,通过使用 FPGA,所有这些软件开发工作都能够在流片前完成,从而大大加快各种最终产品的开发进度。

Freescale构建了一个多芯片系统的原型,其中包括一个双核MXC2基带处理器和一个RF收发器芯片的数字部分。基带处理器内置一个用于调制解调器处理的Freescale StarCore DSP内核、一个用于用户应用处理的ARM 926内核,以及 60多个外设。

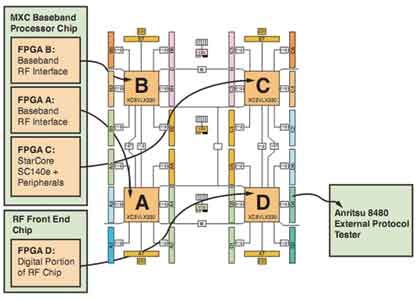

Synopsys HAPS-54原型板用来实现原型(如图3所示)。该基带处理器有500多万个ASIC门,Scott的团队使用Synopsys Certify工具将其在原型板上划分给3个赛灵思Virtex-5 FPGA,同时把数字RF设计布置在第四个FPGA中。Freescale 决定不构建模拟部分的原型,而是直接从Antritsu协议测试盒中以数字形式提供移动网络数据。

图3 Freescale的SoC设计在HAPS-54原型板上的分区

较早的内核使用的某些设计技术对ASIC来说非常有效果,但对FPGA来说却不太好用。另外,RTL的一部分是从系统级设计代码中自动生成的,由于其过于复杂的时钟网络,对FPGA来说也是相当不利的。因此,必须对RTL进行一些调整,使其更加兼容FPGA,这样做的成效非常显著。

仅在完成首个芯片后一个月,Freescale团队就成功地从这个系统中拨出了第一个移动电话呼叫,把产品开发进度缩短了6个多月,这非常具有里程碑式的意义。

这个例子说明基于 FPGA的原型方法能够给软件开发团队提供什么样的增值工具,能够在产品质量和项目进程方面带来怎样显著的回报。

接口优势:测试真实条件下的数据效应

很难想象有这样一种 SoC 设计可以不遵守输入数据、处理数据、生成输出数据的基本结构。实际上,如果我们深入SoC设计,就会发现无数的子模块遵循着同样的结构,直到单个门级。

要在这些层级中的每一个层级验证正确的处理,要求我们提供完整的输入数据集,并观察处理结果的输出数据是否正确。对单个门来说,这个工作很简单,对小型 RTL 模块来说,也是可能的。但随着系统日趋复杂,从统计上来说基本没有可能确保输入数据和初始条件的完整性,尤其是在有软件运行在一个以上的处理器的时候。

最后一点非常重要,因为不可预测的输入数据能扰乱

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)