基于DDS的高精度任意波形发生器设计

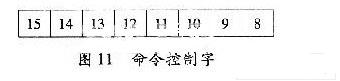

当RS232发送数据完成时,接收数据处理模块立即从地址0x00000开始读取RAM中的数据。当第1个数据和第2个数据分别为 16'hAAF0和16' hBB55时,则第3个数据的高8位为命令控制字,否则接收数据处理模块停止读取RAM中的数据。8位命令控制字各位所代表含义如下

用A代表命令控制字,A[n]代表命令控制字的第n位数据,则:

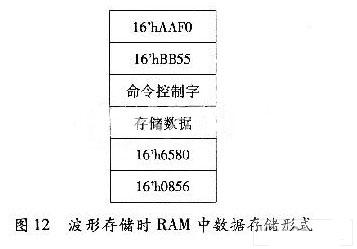

当A[15]为1时表示存储用户自定义波形数据,为0时表示任意波形的产生。当为波形存储时,A[14:8]为0表示将波形数据存入用户自定义 1区,为1表示存入2区,为3表示存入3区,为4表示存入4区。从读取的第4个数据开始即为用户自定义波形数据,共65 536个,再以16'h65 80和16'h0856作为结尾,其存储形式如图12所示。

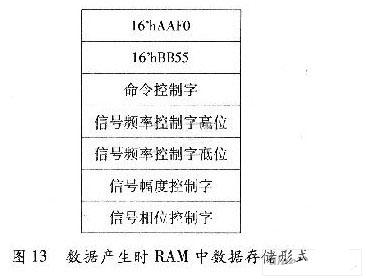

当为任意波形产生时,A[14:11]为0表示产生正弦波;为2表示产生方波;为3表示产生三角波;为4表示产生锯齿波;为5表示产生高斯白噪声;为6表示产生用户自定义1区波形;为7表示产生用户自定义2区波形;为8表示产生用户自定义3区波形;为9表示产生用户自定义4区波形。从RAM中读取的4个16位数据分别代表要产生波形的频率(32位)、幅度、相位(方波时为占空比)控制字。其数据存储形式如图13所示。

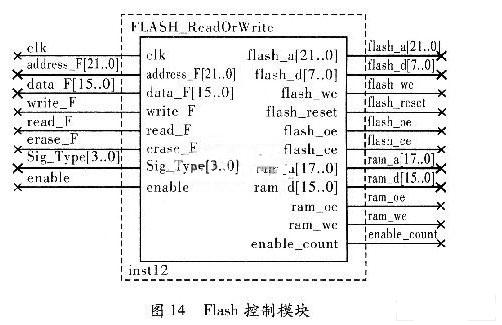

4.3 FLASH数据存取模块设计

此模块用于波形数据的存储和读取。在信号产生模式时,它根据Sig_Type[3:0]输入的数据判断需产生的波形,再从FLASH中读取对应波形的数据信息并存入RAM中。当Sig_Type[3:0]为1时表示产生正弦波;为2时表示产生方波;为3时表示产生三角波;为4时表示产生锯齿波;为5时表示产生高斯白噪声;为6时表示产生用户自定义l区波形;为7时表示产生用户自定义2区波形;为8时表示产生用户自定义3区波形;为9时表示产生用户自定义4区波形。

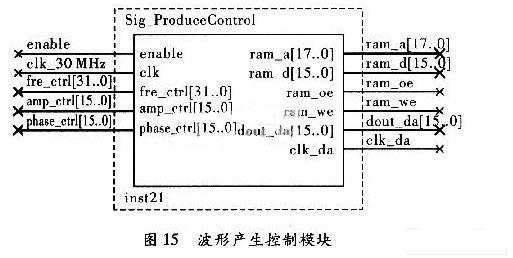

4.4 波形产生控制模块

模块利用DDS技术控制AD768产生任意波形信号,如图15所示。

fre_ctrl,amp_ctrl,phase_ctrl分别为波形的频率控制字、幅度控制字和相位控制字。clk为此模块的控制时钟,它的 6分频时钟为32位相位累加器时钟。在一个相位累加器时钟周期内,模块以累加器的高16位累加值、相位控制字及18'h20000之和作为RAM地址,从 RAM中读取波形信号的数据,设此数据为data,则D/A输出的数据为,然后再在clk_da的上升沿将此数据送入AD768,依次循环,则AD768 的输出将产生阶梯状的信号波形,再经过低通滤波器和功率放大器即可得要产生的波形,图16为系统产生的5V、200kHz正弦信号。

5 结束语

完成了任意波形发生器的设计,完成了系统硬件路的设计及软件编程,经测试,系统可产生50Hz~200kHz频带内的正弦波、方波、锯齿波、三角波、高斯白噪声等常用信号,该信号发生器具有频率分辨率高,频率转换速度快、信号纯度高、产生信号种类多等优点。可广泛应用于通信系统、自动控制系统、仪器仪表、电子对抗及遥控遥测等领域。

- DDS函数信号发生器的优点(09-28)

- 基于DSP与AD9852的任意信号发生器 (11-03)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于AD9858的线性调频源设计(11-03)

- 基于DDS的高分辨率信号发生器的实现(11-04)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)