基于DDS的高精度任意波形发生器设计

随着数字信号处理技术的飞速发展,高精度大动态范围D/A转换器的出现和广泛应用,基于取样技术和计算技术,通过数字方法生成频率和相位相对固定且可调的合成技术,即直接数字频率合成(DDS)技术日益成熟,它采用全数字化结构,具有频率分辨率高、相对带宽宽、频率转换速度快、相位噪声低、信号纯度高等优点。因此,本系统采用DDS技术来完成任意波形发生器设计。

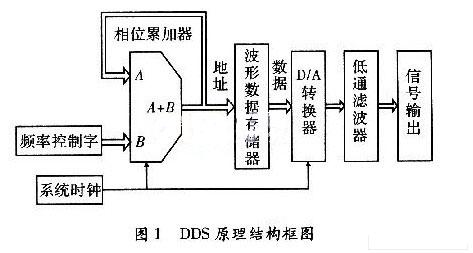

1 DDS工作原理

直接数字频率合成(DDS)技术是一种以采样定理为基础的全数字化波形产生方法。DDS频率合成器主要由相位累加器、波形数据存储器、D/A转换器和低通滤波器组成,其原理框图如图1所示。在一个系统时钟周期内,相位累加器将前一次的累加值与频率控制字相加,得到新的累加值,将新的累加值作为地址,从波形数据存储器中读取信号的幅度值,送入D/A转换器将数字信号转换为模拟信号,最后再经低通滤波器生成需要波形。其中波形数据存储器中存储了周期信号单个周期的幅度值,相位累加器每溢出1次,可从波形数据存储器中读取1个周期的信号幅度值。因此,若假设频率控制字为K,相位累加器为N位,则经过个系统时钟周期,可产生1个周期的输出信号,再设系统时钟频率为fsclk,则输出信号频率。

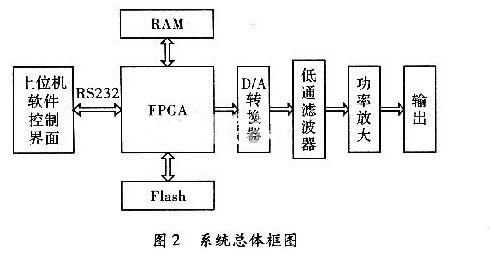

2 系统总体框图

系统总体框图如图2所示。其中,上位机软件由LabWindows软件编写,用于控制信号的产生,下位机以FPGA作为核心控制器件,主要用于接收上位机发送的控制命令和信号参数,并控制下位机系统产生对应波形。下位机系统主要分为FPGA控制单元、波形存储单元、波形产生单元。波形存储单元主要包括FLASH和SRAM,FLASH用于存储各种波形数据,波形产生时,FPGA先将要产生的波形数据从FLASH读入SRAM,再利用相位累加器的累加值从SRAM中读取波形数据。波形产生单元主要完成波形数据的产生,首先将SRAM读出的波形幅度数据送入D/A转换器,产生信号的阶梯序列波,再通过低通滤波器和功率放大电路产生输出信号。

3 系统硬件设计

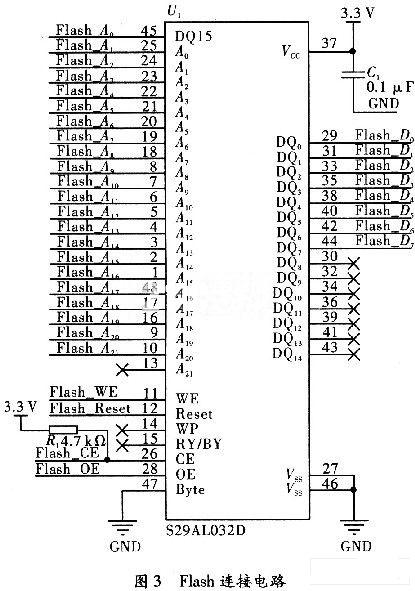

3.1 FLASH连接电路图

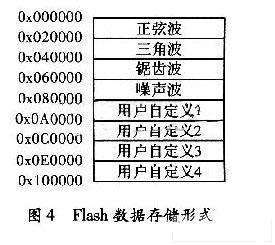

FLASH采用美国飞索半导体公司的S29AL032D,其容量为32 MB,它用于存储各种波形的幅度信息,其存储形式如图4所示。

由图4可知,地址区间0x000000~0x01FFFF存储正弦波幅度值,地址区间0x020000~0x03FFFF存储三角波数据,地址区间0x040000~0x05FFFF存储锯齿波数据,地址区间0x060000~0x07FFFF存储白噪声数据,地址区间 0x080000~0x0FFFFF为4个用户自定义区,存储4种用户需产生的周期波形数据。

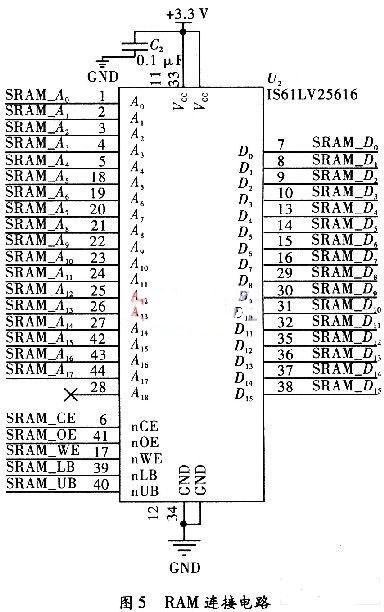

3.2 RAM连接电路图

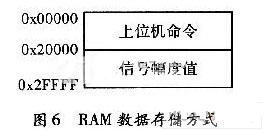

RAM采用美国芯成半导体公司的IS61LV25616AL-10T,其容量为256×103×16 bit,主要用于存储上位机发送的控制命令及波形产生时信号的幅度值,其存储形式如图6所示。

地址区间Ox00000~0x1FFFF存储上位机发送给下位机的控制命令和数据参数,地址区间Ox20000~Ox2FFFF存储系统要产生信号的波形幅度值。

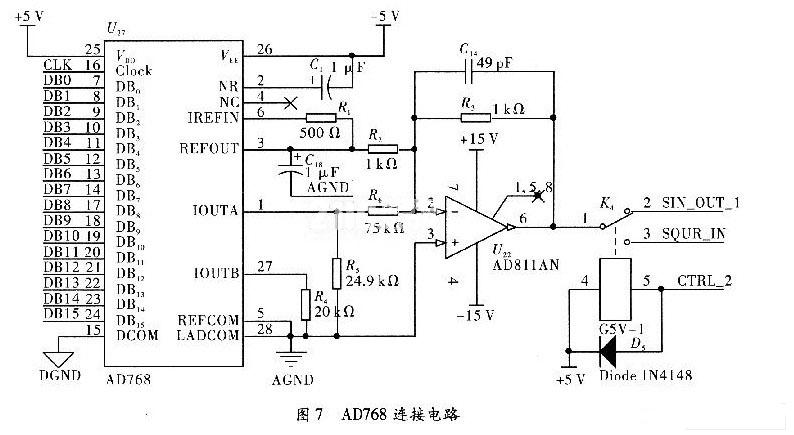

3.3 信号产生电路连接图

图7为任意信号产生的电路连接图,产生信号频率范围为50 Hz~200 kHz。其中,AD768为16位高精度D/A转换器,其最大更新速率可达40Msps,满足设计要求。

4 系统软件设计

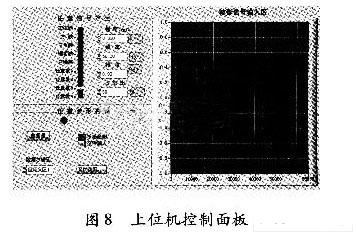

4.1 上位机软件设计

上位机部分由Labwindows软件编写,主要负责对下位机系统的控制,包括对信号频率、幅度、相位(占空比)的设置,信号波形的选择,用户自定义波形数据的输入等,其控制面板如图8所示。

4.2 FPGA软件设计

FPGA为系统的核心控制单元,负责与上位机软件通信及控制下位机系统产生任意波形。

4.2.1 与上位机通信模块设计

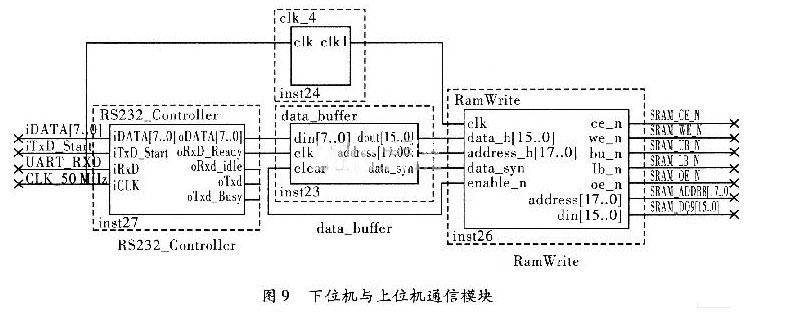

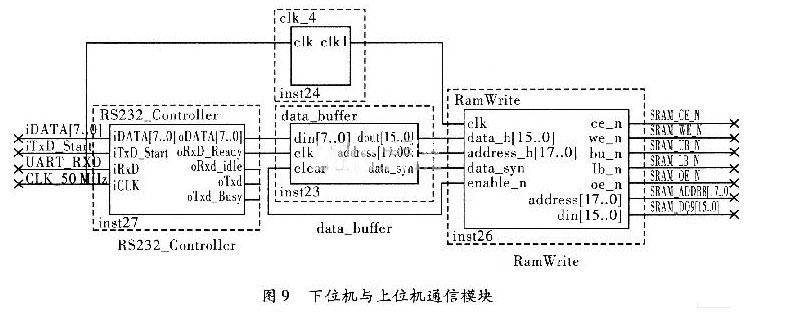

上位机与下位机的通信是通过RS232来实现的,FPGA主要用于接收RS232发送过来的数据并将其存入外部RAM中,通信模块如图9所示。

RS232_Controller模块用于接收上位机发送过来的数据,RS232的速率为115.200 kB/s,8位数据位,1位停止位,无校验位。data_bu-ffer将RS232_Controller接收的数据缓存,并按接收先后顺序组合成16 位数据后送入RamWrite。RamWrite再将这些16位数据从地址0x00000开始存入外部RAM中。

4.2.2 接收数据处理模块

本模块主要用于分析和处理接收到的上位机数据,从中提取出信号的数据信息、各项参数及控制命令,如图10所示。

当RS232发送数据完成时,接收数据处理模块立即从地址0x00000开始读取RAM中的数据。当第1个数据和第2个数据分别为 16'hAAF0和16' hBB55时,则第3个数据的高8位为命令控制字,否则接收数据处理模块停止读取RAM中的数据。8位命令控制字各位所代表含义如下

当RS232发送数据完成时,接收数据处理模块立即从地址0x00000开始读取RAM中的数据。当第1个数据和第2个数据分别为 16'h

- DDS函数信号发生器的优点(09-28)

- 基于DSP与AD9852的任意信号发生器 (11-03)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于AD9858的线性调频源设计(11-03)

- 基于DDS的高分辨率信号发生器的实现(11-04)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)