数字测试仪下的参数测试单元的设计

图5 参数测试流程

2 测试流程

流程说明:测量单元进入测量模式,同时检测是否得到FIPMU或者FVPMU命令,当检测到命令时,输出对应信号,同时根据PMUSETFILTER命令中的检测次数,校验输出信号。经过规定次数下的校验无误后,开启相关测试通道进行后级测试。后级测试根据Kelvin原理,对测试通道的传输阻抗先进行预估。根据得到的预估值Z,校对测试电压并最终得到在该测试通道下的准确模拟参数V1。然后根据同样的原理,对其他要求的通道进行预估,得到相应的阻抗预估值Zn,从而最终得到各个测量通道的准确测量参数。需要说明的一点是由于测试是一个连续的过程,因而每个测量通道阻抗的预估在一整套多芯片的测量中只需要一次。而不必对每个芯片引脚的测试通道反复预估,这样可以节约测试时间和成本。

试验分析

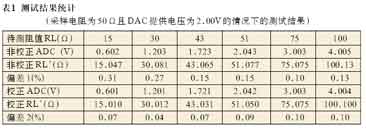

为了验证参数测量单元在负载为小电阻情况下的工作情况,笔者在常温环境下针对不同阻抗的待测单元,分别用无校准IC参数测试单元和校准后的参数测试单元进行测试比对,测试结果如表1所示:校准后的测量单元借助Kelvin技术在小电阻测量的优势,能够在低于50Ω的负载测量中,保持至少提升一个数量级的测量精度优势。而当电阻提高越多,精度优势就越不明显。

根据Kelvin技术的理论可以知道其优势主要在于可以有效评估传输线阻抗带来的测量误差。而当传输线阻抗一定,负载增大时,传输线阻抗造成的压降占总测试电压的比例下降,测试精度的提升程度也会随之下降。

结束语

针对数字测试中面临的参数测试要求,本文提出了基于FPGA控制,32位PCI通信同时具备高精度输出和采样芯片的参数测量单元,并对实现过程中的具体问题进行了分析。

- 数字测试仪的各参数测试单元的设计(10-10)

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)