Laplacian图像边缘检测器的FPGA实现研究

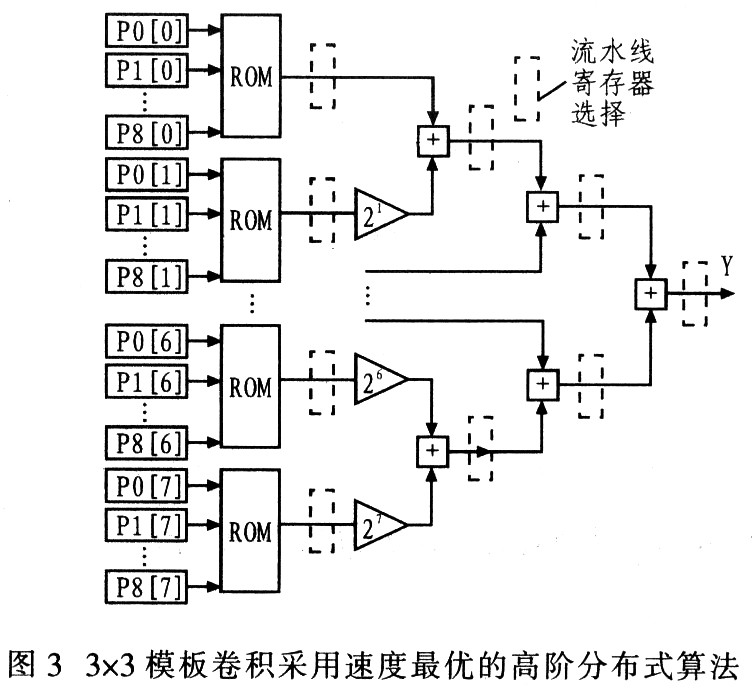

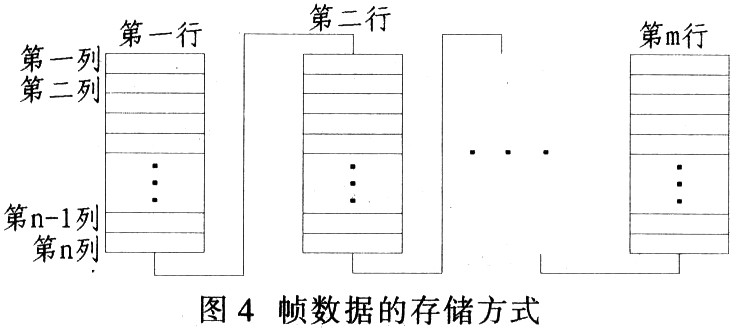

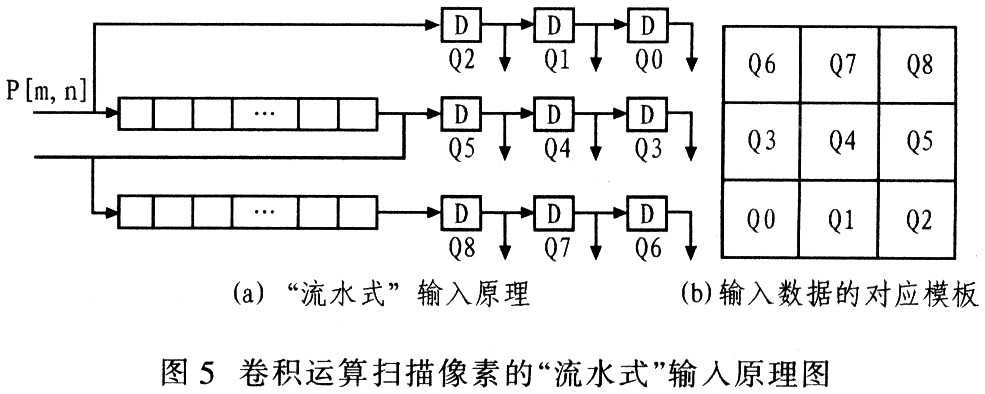

对于该卷积运算的实现,采用前述的"速度最优的高阶分布式算法",其硬件实现的原理框图如图3所示。它是完全流水线式字并行结构,能够达到最大的运算速度。其中的8个ROM是用于实现9个R图位的数相乘,每个ROM都实现一个9位的查找表的功能。5.3卷积运算数据"流水线"输入模块的设计图像的像素是由CCD(或CMOS)摄像机经A/D转换,再经量化而得到,并放入帧存储器。在图像中,整幅图像像素以帧为单位进行存储。每一帧数据的存储方式如图4所示。卷积运算扫描像素的获取如图5所示,该数据输入方式,使用了两个32位的移位寄存器存放像素值,避免了卷积运算中对存储器数据的高度重复读取,使用9个寄存器实现了数据由串行到并行的转换,实现了完全"流水线"的输入方式。

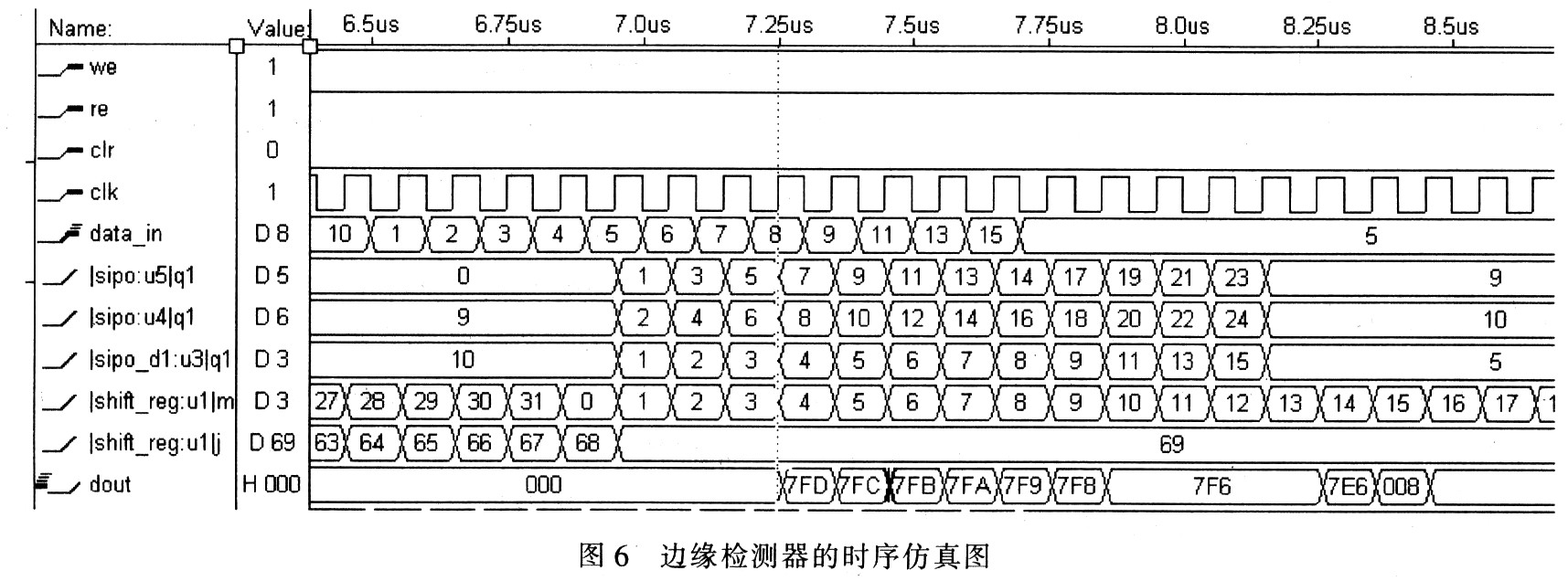

5.4 系统的仿真结果

根据前述的总体设计方案,使用VHDL设计进行各个模块和系统总体程序,选择的FPGA为ALTERA/FLEX/EPF10K20TC144-3,使用的开发工具是MAX+plus II 10.0。图6是边缘检测器的时序仿真图(钟频率10 MHz),由波形仿真结果分析可知,系统达到了设计功能要求,该系统经过初始的两行行延迟和串并转化后(为72个时钟周期),以后每个时钟周期就可"流水式"输出一个处理结果,若系统时钟周期TCLK,对于像素为N个点的数字图像,系统的处理时间TN=70xTCLK+N×TCLK。处理一幅1 024x1 024的图像的时间,当系统时钟为10MHz时,仅需0.1 s,而系统时钟为10 MHz时,仅需0.Ol s。

6 结语

在Laplacian图像边缘检测器的设计中,采用了速度最优的高阶分布式算法(DA)完成模板的卷积运算,使用两个32位的移位寄存器存放像素值,避免了卷积运算中对存储器数据的高度重复读取,使用9个寄存器实现数据由串行到并行的转换,实现了完全"流水线"的数据输入方式,从而在资源.速度上达到了较好的优化,具有良好的实时处理性能。若系统工作时钟为100 MHz,则处理一幅1 024x1 024的图像的时间仅需0.01 s左右。"流水线"的数据输入方式和分布式卷积运算的设计思想,对于数字图像和数字信号处理的FPGA硬件实现,具有广泛的推广应用价值。

分布式算法早在1973年就被Croisier提出,直到FPGA出现,才被广泛地应用在FPGA中计算乘积和。除了用于卷积运算,还用于相关DFT和RNS反演映射的运算。介绍DA算法的运算原理。一个线性时不变网络的输出用下式表示:

常见的边缘检测算子有:Roberts,Laplacian,Kirseh,So-bel,Prewitt等。各种检测算子各有其优缺点,其中Laplacian算子是一种典型的边缘检测方法,它是一个3×3模板,对实现硬件的要求不高,用于检测屋顶型边缘的效果也不错。研究其硬件实现具有一定的典型性,可推广到对其他算子的硬件实现。

- 基于数字图像处理技术的集成块姿态检测(02-27)

- 基于图像处理的型坯直径非接触测量方法研究设计(07-13)

- FPGA在高清图像处理中的重要应用 (10-15)

- 基于数据拟合的激光焊接焊缝图像表面缺陷检测(07-18)

- 基于虚拟仪器的运动位移测量系统的实现(07-26)

- 基于CNN的海空目标检测(03-17)