基于DDS的8051F330啭音信号发生器

时间:01-16

来源:何万库,李会江

点击:

2.5 可调性控制

2.5.1 强度控制

通过设置IDAOH将D/A转换器的满程输出电流,配置为2 mA,结合P01口外接电阻可知,该I/O口的最大输出电压为2x10-3V。由上述可知,改变啭音强度的方法有:①配置D/A转换器,使POI口的输出满程电流为1 mA;②改变电阻R;③设置一个小于1的系数m,将其与存放啭音幅值的数组X[n]相乘,这就相当于改变了波形采样中的最大幅值。

2.5.2 频率控制

中心频率不同的啭音信号对应不同的高截止频率和低截止频率,通过输出构成不同啭音信号的单周期纯音信号,以达到控制频率的目的。

3 扩展与优化

对该系统进行扩展时.可将信号对应的全部幅值存储在单片机中,通过D/A转换器输出所要求的声音。由于单片机存储容量的局限性,大大限制了可存储的最大数据量。但是,可根据需求采用适当的存储器予以扩展。但在利用外部存储器时,应注意若硬性提高DDS参考周期,会限制可产生啭音的最大频率。

4 实验结论

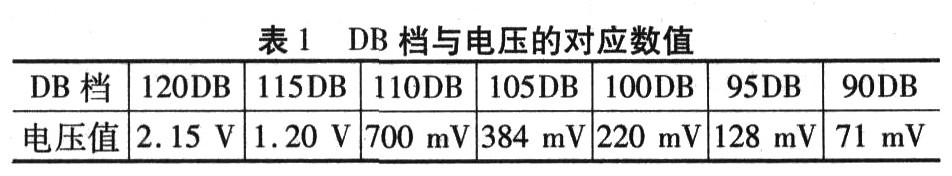

设定以5 dB为步进的衰减,即可由201g(U/U1)=5(U为输出电压;U1为输入电压)得到电压的衰减系数为10025,t通过在衰减前的电压乘以该系数即可获得要输出的声音强度。经过测试,该系统的精度值可达到1 dB。表1给出步进5 dB所对应的电压值。

5 结语

该系统设计精度高,杂音少,结构简单,成本较低,利用软件编程即可实现dB档的衰减,大大简化系统的硬件电路设计。利用软件编程使其具有良好的复制性,无需改动硬件电路就可用作其他声音信号发生器,同时还可方便地扩展。

- DDS函数信号发生器的优点(09-28)

- 基于DSP与AD9852的任意信号发生器 (11-03)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于AD9858的线性调频源设计(11-03)

- 基于DDS的高分辨率信号发生器的实现(11-04)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)