基于DDS的8051F330啭音信号发生器

1 引言

啭音指纯音信号在某一中心频率处所发生音调高低的连续周期性变化,是一种调频信号,听起来不像纯音信号的调高一成不变。在听力学测试中,应用啭音有两个方面的优点:一是啭音更能引人注意。并提高小儿对声音的兴趣;二是应用啭音可减少驻波的产生,从而成为一种重要的测试声。传统产生啭音的系统采用集成电路。因其强度和频率的可调性差,结构复杂,从而提出了一种结构简单,可调性较高的啭音发生器。该发生器基于DDS造波原理,并利用软件编程,采用8051单片机作为主控制器来实现。

2 啭音信号发生器的原理

2.1 啭音波形的简化处理

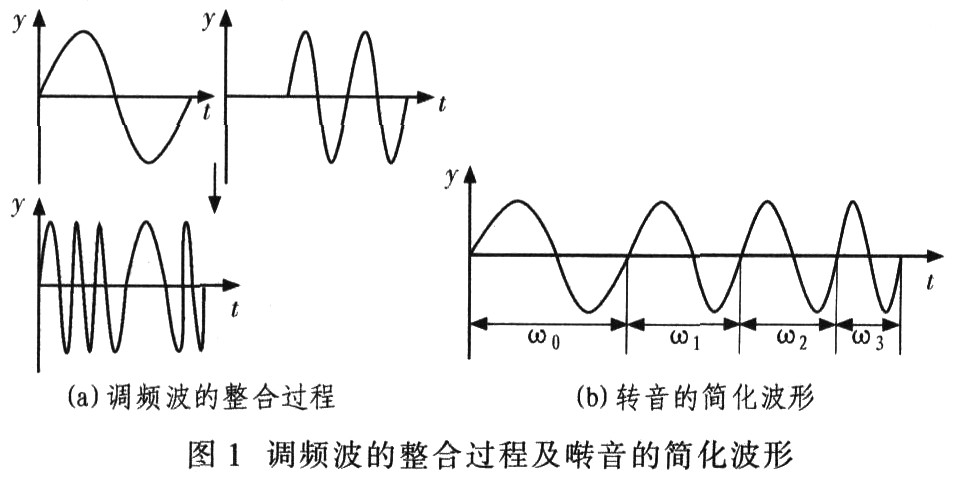

频率调制是用低频调制信号控制高频载波频率信号的过程。调频过程中载波幅值保持不变,载波频率随调制信号的幅值成正比变化。啭音实质上就是一调频波,即用5 Hz正弦波作为调制波,以调制更高频率的正弦载波而得到的信号,其整合过程如图1a所示。正弦载波的公式为:

sin[(ω0+msin(ωo,t1))t2] (1)

式中:ω0为载波角频率;ωc为调频波角频率;m为调频系数,按实际选取,以确定调频波频率范围;t1,t2为不同时间值。但在利用式(1)构造啭音波形时无法确定t1,t2的取值,所以这种方法不可取。

由式(1)可知,msin(ωct1)的取值范围为[-m,m],中心频率为ω0时,其调制波信号的频率范围为[ω0-m,ω0+m]。中心频率确定的啭音信号波形由上截止频率、下截止频率和中间频率的纯音波形构成。根据啭音波形的构造特点,对其简化处理,将组成啭音波形的纯音信号按频率低到高依次排列,即可得图1b所示的简化波形。由图1b可知,频率为ω的啭音信号可由角频率ω0~ω3的纯音信号依次进行衔接构成。该信号发生器的主要设计思路是以上述原理为依据.首先构造出单个频率的纯音信号所对应的一个周期波形,然后将上述4种角频率的单周期纯音信号进行积木式叠加.最后输出这一整块积木,进而得到对应频率的啭音信号。

2.2 DDS技术简介

图2给出DDS原理框图。在对信号数字合成时,从初始相位开始,每隔固定时间以一定的相位增量改变一次相位.并将对应的信号幅值写入D/A转换器。通过相位累加器在固定参考时钟的控制下累加实现相位的改变。累加器溢出后完成一个周期的相位改变,D/A转换器输出一个周期的阶梯信号,以通过低通滤波器得到平滑的输出信号。通过改变相位增量(简称频率字)来改变累加器的溢出速度,从而实现对输出频率的调节。

式中;f0为输出频率信号;fs为参考时钟频率,反映波形离散点的发送速率;k为频率字;n为相位累加器字长;△f为输出信号频率分辨率。

通常按查表法进行相幅转换。由于波形数据有限,一般只能取相位累加器的高位m作为查表指针。后位(n-m)可视为小数部分,在下次求和时予以累计。该信号发生器中所应用的与固定频率纯音信号对应的一个周期的波形就是根据上述原理构造的。由式(2)知,k=2nfo/fs。当系统要输出fo纯音信号时。因系统中fs固定,待选定相位累加字长后,即可通过上式求得对应的频率字K,这就是通常意义上的步长。

2.3 硬件电路设计

该发生器采用8051F330单片机作为主控制器:采用外部晶振11.059 2 MHz作为振荡器:将P01口配置为模拟输出,并作为D/A转换器的输出口。以1.2 V为基准,通过OP07对信号电压放大:通过TIPl22和TIPl27组合成推挽方式对信号电流放大,以驱动耳机,产生人耳能识别的啭音。OP07是一种精密、低噪声和低漂移的运算放大器,内部有短路保护机制,用以防止负载短路时损坏器件。二极管VD3,VD4用来向TIPl22和TIPl27提供偏置电压,以消除交越失真。为了消除电源信号中的高频噪声,采用RC高通滤波器电路和低通滤波电路对系统中的高、低频噪声进行信号处理。图3给出系统硬件电路图。

2.4 软件设计

2.4.1 上位机编程

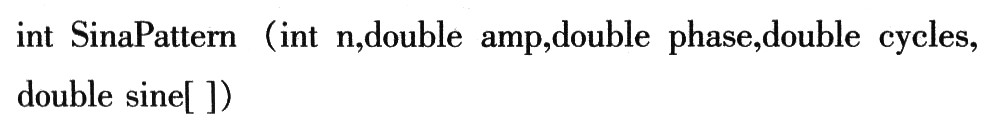

CVI作为一个用于建立自动测试系统的理想软件开发系统,提供了大量用于信号分析和处理的函数,极大地满足了工程人员的需要。CVI中信号的产生库位于Library-Advanced Analysis-Signal Generation下,可以产生冲击、脉冲、斜坡、正弦、噪声及三角波等信号,利用数学方法产生所需信号的离散数据序列。

//产生一个正弦信号波形数据,并把数据存放在sine[]数组中。phase:初始相位值。若要产生正弦信号。则相位值为90°,默认值为0;sine[]:输出波形数组,离散数值存放在该数组

2.4.2 下位机编程

下位机采用C语言中嵌入汇编语言方式输出波形,既可利用C语言控制方便和形象化的优点,也可利用汇编语言清晰简洁的工作流程,提高DDS的参考频率。

- DDS函数信号发生器的优点(09-28)

- 基于DSP与AD9852的任意信号发生器 (11-03)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于AD9858的线性调频源设计(11-03)

- 基于DDS的高分辨率信号发生器的实现(11-04)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)