基于单片机和CPLD的数字频率计的设计

时间:01-27

来源:作者:安徽经济管理学院 张青林

点击:

(1)在CLR端加正脉冲信号完成测试电路状态的初始化。

(2)由预置门控信号将STROBE置高电平,预置门开始定时,此时由被测信号的上沿打开计数器COUNT,同时对基准频率信号和被测信号进行计数。

(3)顶置门定时结束信号把STROBE置为低电平(由单片机来完成),在被测信号的下一个脉冲的上沿到来时,COUNT停止计数。

(4)计数结束后,ED1端输出低电平来指示测量计数结束,单片机得到此信号后,即可利用SS0,SS1进行选择,四次分别读回COUNT中基准频率信号和被测信号计数值,并根据上述测量公式进行运算,计算出被测信号的频率或周期值。

系统软件设计

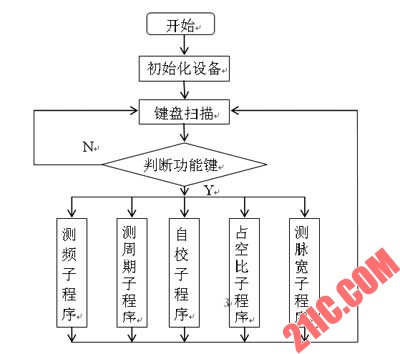

本系统的单片机主控及其外围电路模块用Keil C语言编写,软件模块对应于硬件电路的每一个部分,还包括部分数据计算和转换模块。CPLD模块用VHDL语言编写,并在Max+PlusⅡ平台上,完成CPLD的软件设计、编译、调试、仿真和下载。系统初始化后,主程序不断扫描键盘子程序,当其键按下时,程序跳转到相应的子程序执行其功能,然后返回继续执行键盘扫描主程序。其主程序流程图如图5所示。

图5 系统主程序流程

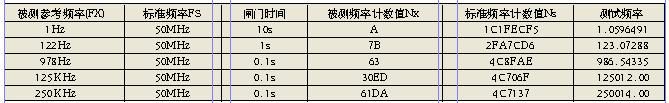

试验测试的结果如表1所示。

结论

本文将智能控制灵活、逻辑运算能力强的单片机和集成度高、运算速度快的CPLD相结合,突破了传统电子系统设计的瓶颈,使设计的系统具有结构紧凑、体积小,可靠性高,测频范围宽、精度高等优点。它可作为独立的仪表使用,也可用做其他仪器仪表的组成部分。

- 基于DDS的高分辨率信号发生器的实现(11-04)

- 基于CPLD和89S51的多功能信号测量仪(10-04)

- 基于MCU+CPLD的相位差和频率的测量方法研究及实现(01-16)

- 脉冲信号源的CPLD实现方法(02-27)

- CPLD 在线缆快速测试技术中的应用(03-01)

- 用于胎儿心电信号测量的嵌入式数据处理系统研究(03-10)