基于MCU+CPLD的相位差和频率的测量方法研究及实现

1 引言

相位检测是电力系统自动控制和谐波分析与控制的关键技术。传统的相位测量是利用过零电路把输入的两路信号(电压或电流)转换为方波信号,再利用逻辑电路和单片机技术对信号某一特殊区段计数和数学变换,求得相位差。随着可编程器件(FPGA,CPLD)的快速发展,目前采用以MCU+FPGA/CPLD为核心的设计理念。这种混合设汁方案利用CPLD在线修改的特点,实现各种复杂数字逻辑设计,结合单片机的控制功能。简化数字电路系统设计,大大缩短系统研制开发周期。本文采用MCU+CPLD设计方法,测量两路信号的相对宽度,充分利用CPLD速度快,单片机控制和数据处理能力强的优势,完成频率和相位差的测量和显示,大大简化了硬件电路,并提高了测量精度和抗干扰能力。

2频率和相位测量原理

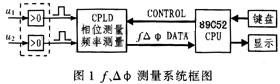

频率测量可先测周期T,然后根据公式f=1/T算出频率,这种方法为间接测量。根据测频的误差分析,在f较低场合,f越低T越大。计数器得数N也越大,±1误差对测量结果的影响减小。具体实现方法是被测信号(正弦)经整形电路后成为方波,用于控制主门的通断,在此期间(一个周期T)外部时标信号TS通过主门,用计数器累计时标脉冲个数。被测信号周期T=NTS,其中TS为时标脉冲周期,N为被测信号一个周期之内累计时的标脉冲个数。相位差△φ对应的时间=N1TS,则△φ=(△T/T)×360°。图1给出f、△φ测量系统框图。

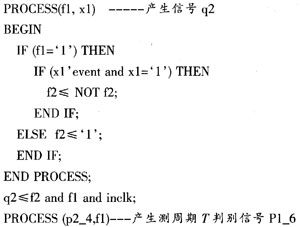

两个频率相同而相位不同的正弦信号u1=Asinwt和u2=Asinw (t+△T)分别送人比较器整形后得到两个方波信号X1、X2。其中X2送入双D触发器的1CLK端,得到图2中的QB波形;同理,利用X1可得到QA波形。最后将QB和QA送人与门74LS11,QB×QA相与得到时间差脉冲△T,△T与相位差对应(△φ=w△T)。

3硬件电路设计

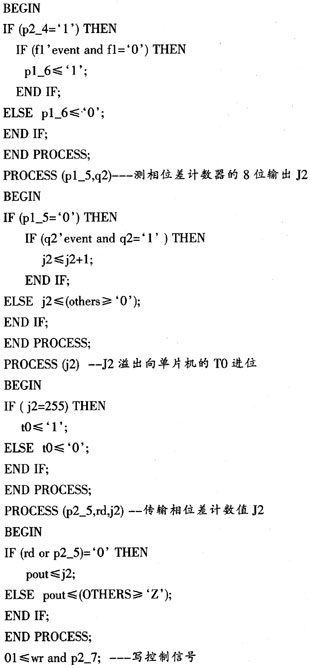

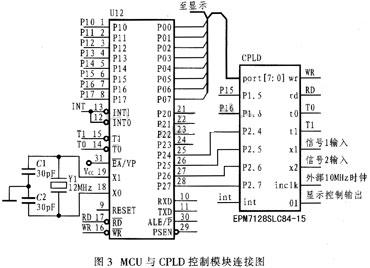

MCU与CPLD控制模块连接如图3所示,MCU采用8位单片机AT89C51,CPLD选用Altera公司MAX7000S系列中的EPM7128SLC84-15,该器件一共有84个引脚,68个I/O端口,采用EEPROM技术,内含2500个逻辑门,128个宏单元。图3中CPLD模块的×1、×2为整形后的被测信号输入端,inclk为外部时标信号输入端,t0、t1端分别与单片机的定时/计数器T0,T1相连,采用单片机内部16位定时/计数器,加上CPLD模块内的8位计数器,可使计数器位数达到24位,以此提高分辨率。P25与读信号RD、P26与RD分别控制两个锁存器74373的数据读取,此外P24、P15、P16分别控制相位和周期的测量。P27与写信号WR控制写显示器,P10、P11、P12、P13、P14用于键盘和显示的控制。单片机P0端口用于从CPLD读取8位计数器数据,另外还用于向显示器写显示数据。

4软件设计

4.1 CPLD控制模块设计

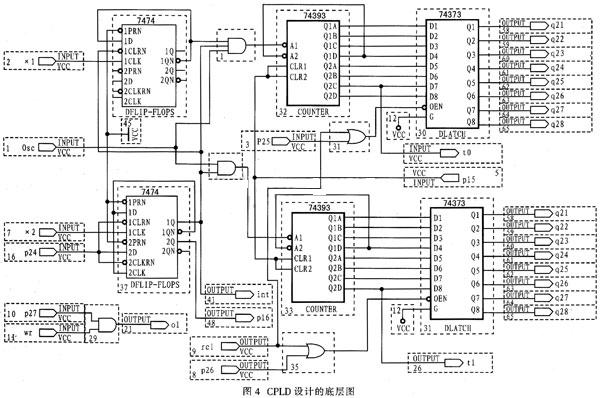

CPLD控制模块的底层没计如图4所示,CPLD控制程序中的变量P2.4、p1.5、×1、×2、p2_6、rd、p2_7、wr的数据类型为IN STD_LOGIC;变量p1_6、t0、t1、o1、pout的数据类型为OUT STD_LOGIC;中间变量有f2、f1、j1、j2、q1,q2,其中f2、f1分别与图2中的波形QA、QB表示的端口一致;j1、j2的数据类型std_logic_vector,分别代表图4中两个8位计数器74393的输出;q1,q2分别表示与门7403、7411的输出。根据频率、相位测量原理,测量部分将由CPLD完成,测量结果经单片机运算后存LED上显示。由CPLD完成的相位测量部分程序以下给出相关程序代码。

4.2 MCU程序设计

系统控制软件采用C语言和汇编语言混合编写,采用模块化设计,各个功能子模块独立。整个软件分为主程序、频率测量子程序、相位差测量子程序。图5为相位差测量子程序流程图。

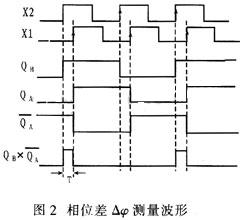

5 CPLD仿真

系统CPLD仿真波形如图6所示,在×1、×2端输入周期T=40μs、相位差△φ=135°的两路被测信号,osc端为5 MHz的输入时标信号。本系统设计实现f、△φ测量,首先要是准确判断出被测信号的一个周期的起始与结束,因此采用单片机P16、P24来完成周期判断。

结合图4的CPLD设计的底层图和图6的CPLD仿真波形分析如下:首先P24=0。使下面的双D触发器清零,即1Q=2Q=0,而且P15=1对两个计数器74393清零,等待计数。P24由0→1后,当被测信号×2上升沿到来时1Q翻转,1Q=1,打开与门7411和7408,允许时标脉冲计数,此时2Q仍为0;当被测信号×2第二次上升沿到来时1Q再次翻转,1Q=0,同时2Q也翻转,2Q=1。此时单片机查询到P16=1,完成一个周期的检测。然后使P24=0,关闭与门7411和7408,停止计数。

计数完毕后,当P25为低电平且RD下降沿到来时,单片机读取第一个锁存器74373的数据为[q28…q211]=01001011;当P26为低电平且RD下降沿到来时,单片机读取第二个锁

- labview相位差测量方法(01-06)

- 浅谈数字化宽带测向系统中的相位差测量及误差(12-26)

- 基于DDS的高分辨率信号发生器的实现(11-04)

- 基于CPLD和89S51的多功能信号测量仪(10-04)

- 基于单片机和CPLD的数字频率计的设计(01-27)

- 脉冲信号源的CPLD实现方法(02-27)