尺寸缩小对沟槽MOSFET性能的影响

0 引言

近几年,随着电子消费产品需求的日益增长,功率MOSFET的需求也越来越大。其中,TMOS由于沟道是垂直方向,在相同面积下,单位元胞的集成度较高,因此导通电阻较低,同时又具有较低的栅-漏电荷密度、较大的电流容量,从而具备了较低的开关损耗及较快的开关速度,被广泛地应用在低压功率领域。

低压TMOS的导通电阻主要是由沟道电阻和外延层电阻所组成,为了降低导通电阻,同时不降低器件其他性能,如漏源击穿电压,最直接的办法是减少相邻元胞的间距,在相同的面积下,增加元胞的集成度。基于此,本文借助了沟槽式接触概念以及突起式多晶硅结构来克服由尺寸缩小引发的沟道穿通效应。最终通过试验,成功开发出栅极电压为4.5 V、工作电流5 A时,Rdson·A为9.5 mΩ·mm2、漏源击穿电压大于20 V、开启电压0.7 V、元胞间距1.4μm的n型TMOS。

1 器件仿真与工艺实现

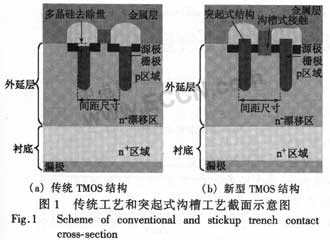

通过图1中传统TMOS的截面图和突起式沟槽工艺截面图的比较,可以看到传统的工艺是利用光刻工艺以掩模版形成器件源区(n+),但是当尺寸不断缩小以后,源区掩模版形成的光刻胶尺寸随之变小,在后续的离子注入工艺中,增加了光刻胶脱落的风险,这就意味着单位元胞中本该被光刻胶掩蔽的有源区会被注入As+离子,从而产生寄生的npn三极管,导致器件工作时漏电增加,严重情况下会导致器件完全失效。本文采用沟槽式接触这一概念,当源区注入时,有源区不保留光刻胶,As+离子完全注入,之后利用接触孔掩模版直接刻蚀掉多余的As+离子注入区域,完全避免了传统工艺下产生寄生npn三极管的风险,如图1(b)中新型TMOS结构所示。

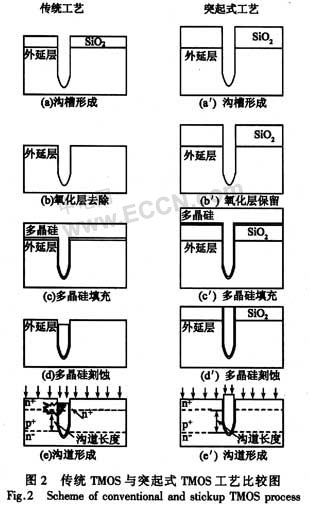

当单位元胞相邻间距为1.4 μm工艺时,由于设计的沟道长度大约为0.5μm,源区结深大致为0.3μm,不得不考虑到传统工艺下源区注入时,多晶硅刻蚀工艺波动所带来的器件性能下降的风险。在传统工艺中,当多晶硅淀积完成后,须通过刻蚀来形成栅极区域,但是多晶硅去除量难以精准控制,同时考虑到刻蚀工艺面内均匀性的特点,Si片内中心与边缘的去除量无法保证相同,从而为随后的源区注人工艺留下了潜在的风险。如图2传统TMOS与突起式TMOS工艺比较图2(e)所示,当源区注入时,如果栅极多晶硅刻蚀量过多,会导致源区高浓度的As+离子从栅极边缘注入到沟道中,间接地减少了沟道长度,从而降低了阈值开启电压(Vth),尤其当沟道长度较短时,甚至会导致器件在正常工作状态时发生漏源间穿通效应,最终导致器件失效。本文采用K·Shenai的突起式结构,在形成沟槽之后,先保留之前所生长的氧化层,然后直接生长栅极氧化膜和多晶硅,在栅极多晶硅形成后,才将先前生长的氧化层去掉,由此便形成了突起式多晶硅结构,从而可以保证在随后的源区As+离子注入时,As+离子无法从沟槽侧壁注入到沟道中,从根本上避免了发生源漏极之间穿通的可能性,降低了器件对刻蚀工艺的依赖程度。这点在器件栅极氧化膜厚度较薄的情况下尤其明显,此时如果采用传统工艺,源区离子注入时,As+离子更容易从侧壁注入到沟道中,从而影响沟道长度。

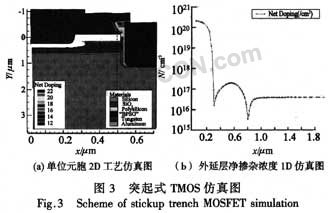

本文通过综合运用沟槽式接触以及突起式结构这两个技术,得到了漏源间击穿电压大于20 V、阈值开启电压0.7 V、栅极击穿电压大于12 V以及在栅极电压4.5 v、工作电流5 A时导通电阻Rdson·A为9.5 mΩ·mm2的n型TMOS。图3是运用SILVACO公司的Athena工艺仿真软件所模拟出来的器件结深示意图以及外延层中的净掺杂离子浓度曲线,可以看出,沟道长度大致0.5μm,源区结深为0.3μm。

2结果与讨论

为了验证这一理论,特别设计了在传统工艺下,栅极顶部到外延层表面的多晶硅去除量(130 nm/230 nm/310 nm)的试验。通过器件的电性能参数比较,如图4(a)所示,可以看到,随着多晶硅去除量的增加,阈值开启电压随之降低,说明了器件沟道有效长度变短,源区离子通过侧壁注入到沟道中,源区结深在沟道表面变深。同时由图4(b)可知,漏源间漏电流也有明显的区别,当多晶硅去除量在310 nm时,从累积概率图中可以看到有部分区域漏电流增大,这一现象随着多晶硅去除量的减少而逐步消失,从而验证了沟道有效长度与多晶硅去除量有很强的相关性。由此可见,为了减少器件性能与刻蚀工艺的相关性,采用突起式多晶硅技术是非常必要的。图5是采用透射电子显微镜所得到的突起式TMOS实际截面图。可以看到在该图中的突起式多晶硅结构以及沟槽式接触,单位元胞相邻间距为1.4μm的n型TMOS,单个芯片有源区面积为0.4 nm2,并采用TSOP6封装。图6(a)、(b)分别是器件击穿电压曲线以及输出特性曲线。由图6(a)可以看到,当漏端漏电流为250μA时,击穿电压为24 V,满足大于20 V的设计需要,由图6(b)可以看到,当栅极开启电压为4.5 v、工作电流为5 A时,对应的导通电阻大致为23.75 mΩ。由于芯片有源区设计尺寸为0.4 mm2,最终Rdson·A为9.5 mΩ·mm2

- 数字存储示波器加快电源设计的验证与测试(01-05)

- 安森美半导体扩充中等电压功率MOSFET系列(10-13)

- 二极管泄漏电流以及MOSFET的亚阈区电流的测量(09-22)

- 精确测量功率MOSFET的导通电阻(11-16)

- 高幅度任意波形/函数发生器简化汽车、半导体、科学和工业应用中的测量(02-20)

- 短沟道MOSFET散粒噪声测试方法研究(07-23)