在线检测与分析快速发现不可见的电学缺陷

BEOL模块结果

BEOL表征使用包含三层金属的CV测试芯片,从Metal 1到Metal 3,包括通孔。通常的SoC产品中,CV设计包括超过1300种不同的布局布线。例如,要表征通孔节距的响应,测试芯片涵盖一系列的结构,这些结构包含了不同的节距,而且不同的顶部和底部金属都有覆盖。另一组结构则找出金属形貌对上层金属短路的影响。这些结构的参数范围和分布是严格设计的,这样获得的ppb级失效结论具有统计学意义,而这个失效级别是先进工艺在使用最少测试晶圆数的条件下所要求的。

完成短流程工艺和通常的线内检查后,在专用的电学测试机中做BEOL CV测试。对每个300mm晶圆而言,其上所有的芯片和结构做测试的时间大概是3小时。用分析软件对电学测试数据分析以确定每类结构的特性,包括失效率、成品率和空间结构图。这样就可以研究缺陷率与布局布线特性或任何其它的可用测量数据的相关性。例如,由下层金属形貌导致Metal 3短路可以被分析,以鉴别和最大缺陷率相关的密度、线宽和线间距。

分析软件也可以只

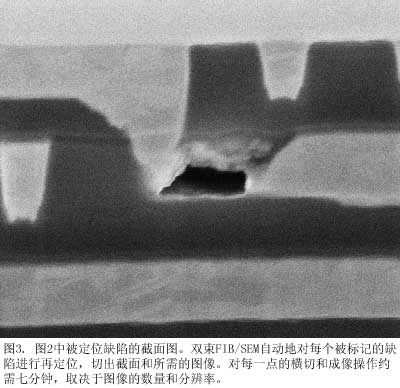

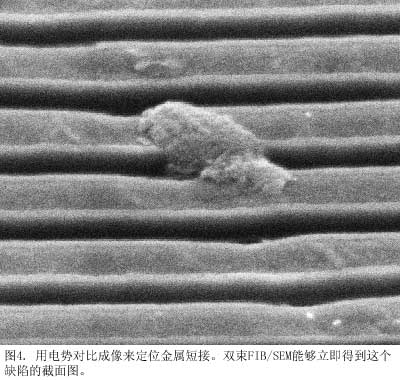

短流程法不仅能探测短路,而且还能探测开路。一般而言,开路(<2 min/site)比短路(<15 min/site)定位更快。图4说明了怎样使用电势对比和FIB技术来隔离金属短接。

多晶硅模块CV表征了浅槽隔离(STI)、多晶硅和金属硅化物模块。他包括一系列用多晶硅在场区和有源区设计的实验,可提供功能和参数特性。然后双束FIB/SEM中的截面与成像有助于找出产生缺陷的根源。

FEOL CV完成接触的扩展特性,这种情况下,金属与局部互连线接触。图5显示了一个开路接触的FIB截面,怀疑是由外部残留物所导致的。尽管这幅截面图中电学断开不是很明显,但是用于定位缺陷的电势对比成像提供了确凿的证据,表明这个接触是开路的。

随着技术节点的不断减小,用传统检测技术不能检测的缺陷比例不断提高。传统不可见缺陷检测方法在晶圆工艺接近完成前是不可用的。延迟不可见缺陷的探测与分析,不仅延长了工艺开发和成品率学习周期,延缓了量产步伐,而且实际上加大了大规模生产的风险。

以上所描述的技术,结合了自动FIB/SEM缺陷分析,可将不可见缺陷探测和分析时间降低一个数量级。严格设计的测试结构对一系列设计参数有优良的敏感性,而且样本数足以在几个ppb级上给出有统计意义的评估。该技术不仅有可靠的致命缺陷探测能力,还有优异的鉴别妨碍缺陷(nuisance defects)的能力。所有这些优点对缩短产品和工艺开发周期,加快可盈利量产步伐,和加速成品率损失的恢复都至关重要。

参考文献

1.Michael B. Schmidt et al., "New Methodology for Ultra-Fast Detection and Reduction of Non-Visual Defects at the 90nm Node and Below Using Comprehensive e-Test Structure Infrastructure and Inline DualBeam FIB," ASMC 2006.

2.D. Ciplickas, S.F. Lee, A. Strojwas, "Critical Features: A New Paradigm for Evaluating IC Yield Loss," Solid State Technology, 2001.

SRAM 相关文章:

- 测量并抑制存储器件中的软误差(10-30)

- 基于J750EX测试系统的SRAM VDSR32M32测试技术研究(07-30)

- 一种采用分离栅极闪存单元实现可编程逻辑阵列的新型测试结构(04-01)