在线检测与分析快速发现不可见的电学缺陷

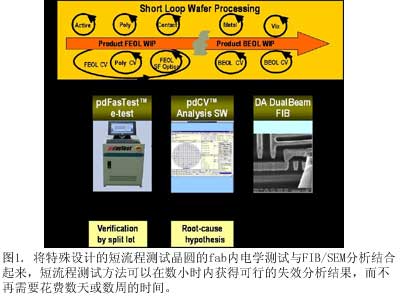

编辑笔记:在Fab里,在经过特别设计的短流程测试晶圆上进行的快速电学测试和自动FIB/SEM缺陷分析可以将不可见缺陷探测与分析的时间降低一个数量级,并且对不同的设计参数非常敏感,因而有足够的样本来做重要的统计评估。

从成品率的角度来看,真正关心的是那些影响成品率的缺陷。其余的缺陷仅仅只是些小麻烦,所以把时间花在它们上面是一种浪费。大部分在线检查和缺陷探测方法都集中在可见缺陷,这样或多或少影响性能。通常,工艺完成以后,只有在电学测试数据获得之后才可能将其与产品成品率进行关联。当然,我们已经知道如何很好地估计哪些可见缺陷是重要的,哪些是与结构和形态无关的。然而,随着器件越来越小,新工艺中引入新结构和新材料,越来越多的致命缺陷是不可见的--指对传统在线检测技术不可见。通常缺陷在形成后,只有经过几天或几周的电学测试才能被找到。

要克服这个不足,人们开发了一种新的在线探测技术,该技术在探测不可见电学缺陷方面比传统的技术要快10倍。另外,该技术获得的电学数据还可以与可见缺陷关联起来,这有助于鉴别致命缺陷和非致命缺陷。已表明,更快的缺陷探测和致因分析能够缩短工艺开发和成品率学习周期,加快量产步伐,加 速成品率恢复,更快将新产品推向市场,提高大规模生产的产量和利润。

可见缺陷探测方法速度很快,几乎能用在产品晶圆制造工艺的任何地方。相比之下,用传统方法探测不可见缺陷有几种局限性:

新技术摆脱了这些限制。它不仅快速,而且能在fab内对特别设计的短流程(short-flow)测试晶圆做电学测量,并使用自动聚焦离子束(FIB)和扫描电子显微镜(SEM)分析,以便在数小时内获得可行的失效分析结果,而不再需要花费数天的时间(图1)。

测试方法

测试晶圆,称为特征载体(CV),含有经过特别设计的测试结构,这些结构对设计工艺间相互作用很敏感,而这些相互作用则影响产品成品率。CV内的测试结构是根据特定的工艺或工艺模块定做的。CV覆盖了大部分FEOL和BEOL出现的问题,而且能完整覆盖系统和随机缺陷,并且只用3到6片晶圆就可得到1-3个ppt失效范围的统计灵敏度。此外,由于CV是短流程测试芯片,设计为几天内制造完成(相比全流程晶圆数月时间),这实际上加快了学习周期。

在超净间内,大量使用CV的专用并行测试机是经过特别设计的,而且比当前参数测试机要快10-15倍。电测试数据自动传送到综合分析软件,该软件能详细表征工艺缺陷模式。该软件将电学数据与所有已知可见缺陷数据做关联,能让操作员从更宽广的属性角度选择与分类缺陷。该软件通过文件接口导出已选择的数据和定位。

在电学测试完成后,有缺陷的晶圆和被测器件的位置数据被传送给一个在线、全晶圆双束FIB/SEM,以便对被选的缺陷做详细的特性分析。双束缺陷分析使用FIB在被选缺陷处切割出截面,暴露出衬底结构以便用SEM做高分辨率成像。需要配备离子和电子束,以使SEM能够对研磨过的FIB截面成像。自动化的高速平台能快速精确地定位截面和成像中的缺陷,靠的是从电学测试机传来的数据。

分析处理分两个阶段。第一阶段,操作员使用电势对比成像(voltage contrast imaging)来识别和精确定位失效位置。电势对比存在于SEM图像中,是由样本表面的电势差引起的。电荷由扫描电子或离子沉积下来,并积累在未接地的非导体表面或导体表面。积累的电荷改变了表面电势以及用来SEM成像的二次电子信号的强度。电势对比图给我们提供了一种快速找出微电子电路短路与开路的方法。缺陷一旦定位,双束FIB/SEM就用FIB自动研磨一个基准标记。在这个研究中,我们可以定位开路缺陷(>100 M-Ω)和短路缺陷(<50 K-Ω)的最大速率约为每小时10处。缺陷的尺度范围从小至50nm以下到大至40,000平方微米。

在第二个分析阶段,双束FIB/SEM自动重访每个被标记的缺陷。利用特征识别程序,它先定位到先前的基准标记处,然后研磨一个精确放置的有缺陷的截面,最后得到衬底结构的高分辨率成像。系统也许还需要交替使用切片-视图法,其中一小部分的晶圆表面以增加的步长被研磨,然后每步后进行成像。每处截面和成像操作大概要花7分钟时间。缺陷分析机把图像上传到电学测试机的分析数据库,然后和特定的缺陷做关联。这些图像可以被存在数据库中的所有其他属性使用,以优先补偿及促使成品率提高。

SRAM 相关文章:

- 测量并抑制存储器件中的软误差(10-30)

- 基于J750EX测试系统的SRAM VDSR32M32测试技术研究(07-30)

- 一种采用分离栅极闪存单元实现可编程逻辑阵列的新型测试结构(04-01)