SoC设计过程中需要考虑的关键测试要素

试插入就可以执行所有的存储器测 试,第二步完成冗余单元的融接。

b) 用于双端口SRAM的软件BIST

通过下载软件和使用处 理器实现BIST算法完成对设计中双端口SRAM的测试。并不是SoC器件中的所有SRAM都可以直接被处理器读写,因此可能还需要额外的逻辑,如 FIFO。虽然一般情况下BIST算法不是太复杂,但仍需要为这种方法在准备软件测试式样方面作出一些努力。然而还需十分小心以确保创建片上MBIST逻 辑时考虑了RAM的硬件版图(图3)。软件方法的优点在于,至少对于大多数SRAM来说,MBIST执行访问的方式和速度与功能访问完全相同。

c) DFM

所有SRAM测试都能创建位故障图(BFM),一般通过CPU的数据总线输出BFM。这些BFM就是基本的DFM,可以为工艺工程师学习和改善良品率提供必要的信息。

DRAM测试

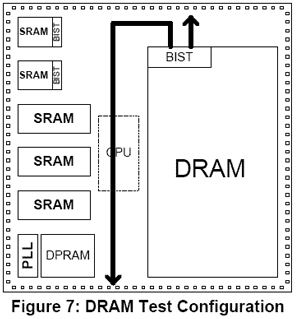

图4:DRAM测试配置。

在 过去几年中,嵌入式DRAM测试一直是重点开发对象,在这个SoC器件中已经实现了相关文献中提及的一些想法。DRAM BIST能够进行内置冗余计算(也被称为BISR(内置自修)),但该功能一般不用。BIST逻辑本身是利用ATPG模式和LSSD扫描寄存器进行测试 的。DRAM配置用于高度并行的测试。DRAM测试时间一般要比逻辑测试时间长得多,因此我们需要重点关注高度并行的测试以减少每个器件的有效测试时间。

嵌 入式DRAM预融接测试是在专门的存储器测试仪上使用直通模式下的BIST完成的(图4)。采用这种方法的原因是可以通过减少冗余修补计算时间和高度并行 测试缩短测试时间。专用存储器测试仪具有一些典型的优势:为存储器测试算法提供硬件支持,为整个数兆存储器提供存储和分析故障位信息的容量,可以为高度并 行测试提供大量充足的电源。

为了方便与存储器ATE一起使用,对本文提及的SoC器件做了适当的修改。为了配置成存储器,该 器件需要最小的测试模式输入(预备序列)。一旦配置好后,就能提供典型的包括可访问冗余数据输入和输出的存储器接口。通过限制地址和数据输入的数量以及在 裸模的二个相向边沿物理定位所有必须的衬垫实现高度并行的测试(图4)。

利用BIST完成DRAM测试

如 前所述,DRAM模块内含一个BIST控制器,可以利用一条IEEE1149.1指令对芯片作出适当配置后激活该控制器(图4)。当融接完成后,可以不用 专门考虑存储器修复即可在标准逻辑ATE上进行DRAM测试。所需的连接数量也有大幅下降,因为BIST可以产生地址和片上控制信号,并产生单次通过/失 败结果。

DFM原理可以用来指导DRAM结构的开发。重点不是限制衬垫的数量和位置,而是使嵌入式存储器具有最大的可控制性 和可观察性,并可以通过JTAG控制器选择最小测试模式入口序列。然而,实际使用的是更宽的控制和数据总线访问,包括裸片各边沿上的衬垫。这种模式适用于 故障分析,在生产测试过程中并不使用,因为SRAM测试同样会创建位故障图,并将它传送给ATE用于进一步分析。

上述SoC 器件中包含有二个环形振荡器,主要用于生产期间的速度测试。这二个环形振荡器的固有周期约为2ns,并各自连接32分频逻辑电路。因此典型的外部周期是 64ns,由此产生的速度就可以用标准的ATE进行测量。为了方便比较走线和门延时效应,通常使用一个具有密集版图的环形振荡器和一个具有人工分布版图的 环形振荡器。环形振荡器的测试结果表明了硅片速度,从而允许用户跟踪工艺变化,并排除速度太慢或太快的器件。

本文小结

本 文主要讨论了一个具有可测性设计和可制造性设计的新型单片系统,同时提出了这样一个集成了嵌入式DRAM和模拟模块以及较常见的数字逻辑和静态RAM的系 统在生产测试中所面临的挑战。为了满足测试要求,需要采取各种不同的策略,同时利用单个标准的IEEE1149.1接口将被测器件配置成各种相应的模式。

将来设计师必须了解更多的测试信息。随着技术和密度的提高,制造商可以在单个芯片中集成更多的单元,设计师只具备扫描和BIST技术的基本知识是远远不够的。为了针对任何特殊器件选出最适合的测试策略,设计师必须通晓各种可能的器件生产测试方法。

作者:Roderick McConnell博士

业务开发高级经理

Infineon Technologies AG

Martin Schrader

数字设计工程师

Infineon Technologies AG

- 嵌入式测试方案及高速测试技术(03-10)

- AFM:应对65nm以下测量技术挑战(11-13)

- 便携式发动机测试设备的研究(05-20)

- DDR测试--SDRAM时钟分析案例(04-10)

- DDR SDRAM在高速数据采集系统中的应用(05-11)