一种实用的VXI总线寄存器基接口电路的设计

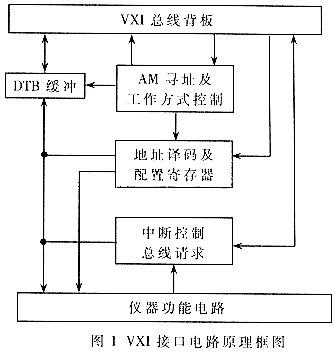

VXI(VMEbus eXtention for Instrumentation)总线是一种完全开放的、适用于各仪器生产厂家的模块化仪器背板总线规范。它具有高速数据传输、结构紧凑、配置灵活、电磁兼容性好等优点,已成为高性能测试系统集成的首选总线。VXI总线器件主要分为:寄存器基器件、消息基器件和存储器基器件。目前寄存器基器件在应用中所占比例最大(约70%),其实现方法在遵守VME协议的前提下,根据实际需要各有不同。VXI接口电路用于实现器件的地址寻址、总线仲裁、中断仲裁和数据交换等。设计VXI接口首先需明确寻址空间和数据线宽度,VXI器件寻址有A16/A24、A16/A32和A16三种。A16/A24寻址支持16M字节空间,A16/A32寻址支持4G字节空间,A16寻址支持64字节地址空间,但不论哪种寻址方式,A16寻址能力是不可缺的。本文设计的VXI寄存器基接口电路是A16寻址的,支持D8和D16数据线传输,有较宽的使用范围。其接口电路原理框图如图1所示。

1 DTB及DTB仲裁

DTB(数据传输总线)及DTB仲裁是VXI接口的核心,DTB主要包括:寻址总线、数据总线和控制总线。其主要任务是:①通过地址修改码(AM)决定寻址空间和数据传输方式。②通过DS0*、DS1*、LWORD*、A1控制数据总线的宽度。③通过总线仲裁决定总线优先使用权。

VXI总线器件在A16(16位地址)寻址时,有64字节的地址空间,其呈部分作为器件配置寄存器地址(已具体指定),其余可用作用户电路端口地址。每个器件的寄存器基地址由器件本身唯一的逻辑地址来确定。地址修改线在DTB周期中允许主模块将附加的器件工作模式信息传递给从模块。地址修改码(AM)共有64种,可分为三类:已定义修改码、保留修改码和用户自定义码。在已定义的地址修改码中又分为三种:①短地址AM码,使用A02~A15地址线;②标准地址AM码,使用A02~A23地址线;③扩展地址AM码,使用A02~A31地址线。A16短地址寻址主要是用来寻址器件I/O端口,其地址修改码为:29H、2DH。

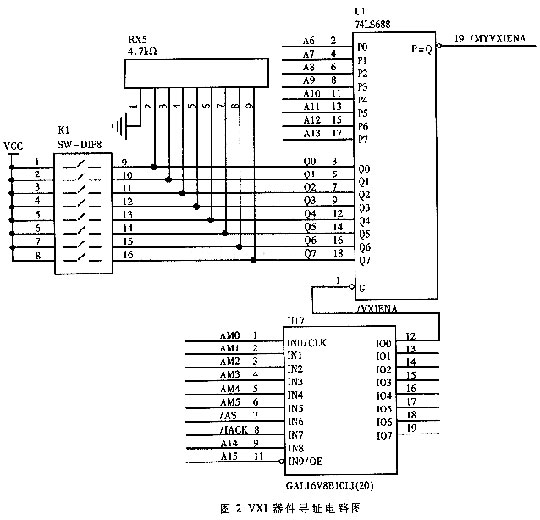

图2为VXI器件寻址电路图,其中U1为可编程逻辑器件,其表达式为:VXIENA*=AS*+!IACK*A14+!A15+!AM5+AM4+!AM3+AM1+!AM0;(!IACK*表示系统无中断请求)。寻址过程为:当VXI主模块发出的地址修改码对应为29或2D、总线上地址A6~A13和逻辑地址设置开关K1的设置相同并且地址允许线AS有效时,图2中的MYVXIENA*有效(为低),表示本器件允许被VXI系统寻址。在允许本器件寻址的基础上(即MYVXIENA*有效),再通过MYVXIENA*、A1~A5、LWORD*、DS0*、DS1*译码生成64字节地址,根据VME总线协议可译出单字节地址和双字节地址。协议协定:当单字节读写时,奇地址DS0*为低、DS1*为高,偶地址DS1*为低、DS0*为高,LWORD*为高;双字节读写时,DS0*和DS1*为低、LWODR*为高;四字节读写时,DS0*、DS1*和LWORD*都为低。

DTB数据传输应答主要依赖DTACK*和DS0*之间的互锁性握手关系,而与数据线上有效数据什么时候出现无关,所以单次读写操作的速度完全决定应答过程。为适应不同速度用户端口读写数据的可靠性,本文采用由用户端口数据准备好线(DATREADY*)去同步DTACK*答应速度的方法来保证数据传输的有效性。该方法的优点是电路简单、使用方便,缺点是占用DTB时间长,影响VXI系统性能,且最长延时时间不得超过20μs。通常情况下用户可通过数据暂存的方法实现数据可靠传输,并使用户端口数据准备好线(DATREADY*)接地。由于寄存器基器件在VXI系统中只能作为从模块使用,所以其总线请求只有该器件发生中断请求时才由中断管理模块提出。

2 中断请求及仲裁电路

VXI系统设有七级中断,优先中断部迟疑不决包括:①中断请求线IRQ1*~IRQ7*;②中断应答线IACK*;③中断应答输入线IACKIN*;④中断应答输出线IACKOUT*。从系统的角度看,在VXI系统中有一个成菊花链的中断查询系统。当VXI系统中有中断请求时,中怕管理器使中断应答信号IACK*有效(置低),并送往菊花链驱动器,菊花链驱动器使输出IACKOUT*有效,送至相邻的下一个器件。如果相邻器件没有中断请求,则该器件的IACKOUT*输出仍为低,继续向下一个相邻器件传送;当此器件有中断请求时,所以其输出IACKOUT*为高,进入中断过程,并屏蔽后级器件的中断应答。

为实现中断请求和中断仲裁,每个器件的中断仲裁电路应完成的功能为:①产生中断请求;②上传状态/识别码;③屏蔽后级中断应答。本文设计的中断仲裁电路如图3所示。其中TX1~TX3来自中断号选择跳线器,INNER-IRQ为器件内部用户电路中断请求信号,上升沿有效。中断请求过程分如下四步:(1)在系统复位或

VXI 相关文章:

- 安捷伦推出L4411A数字万用表(04-23)

- 逻辑分析仪技术专题(05-26)

- 深入分析本土测试测量企业的现状和挑战(07-03)