基于CPLD控制的通用视频采集模块

图2.5 FIFO 读时序控制

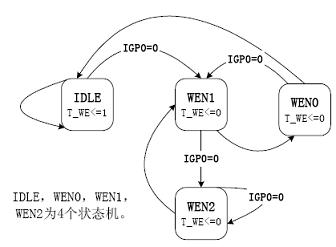

图2.6 CPLD 控制写时序的状态机

从FIFO的写时序图和读时序可以看到,当/WE和/RE(两者都是低电平有效)为高电平的第一个周期,芯片仍然进行写入和读出

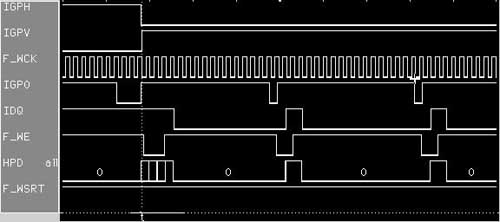

操作,而下一个周期才进入挂起状态。同样,当/WE和/RE由高电平变为低电平时,也是要延后一个时钟周期才能发生改变。这种特性造成在设计SAA7114H向FIFO写入时序的时候,需要提前一个周期确定下一个数据是否为有效数据。CPLD程序中通过检测IGP0(配置为SAA7114H I-port端口的Buffer almost empty flag) 来实现这点。利用逻辑分析仪测出整个写入时序为图2.8。

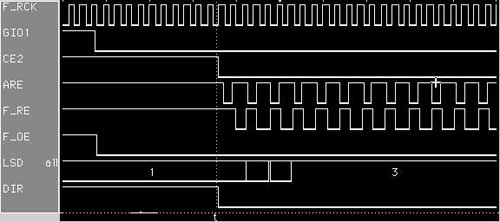

在读控制中主要是产生用于DSP 中断的外部使能,中断DSP 读取FIFO的数据,同时还要通知DSP 读取的是奇数场的数据还是偶数场的数据。FIFO 的读时序图上可以看出如果F_OE 为低电平,这F_RE 变高后(F_OE 和F_RE 都是低电平有效),FIFO 的输出仍然保存原来的值,而不是进入高阻状态。CPLD 控制程序中正是利用这点来实现DSP对FIFO 的读写时序的匹配以及保证DMA 传输在被DSP 中断后不会出错。DSP 的FIFO 的读取采用32 位的异步接口,8个DSP的时钟周期(注意: 采用的是DSP 的主频,不是总线频率ClockOut2) 实现一次对FIFO 的读写。具体设置参考EMIF 总线初始化部分。CPLD通过将F_RE 置高,延长FIFO数据的输出时间来匹配整个DSP 的读取时序。利用逻辑分析仪测得FIFO 的读取时序为图9。

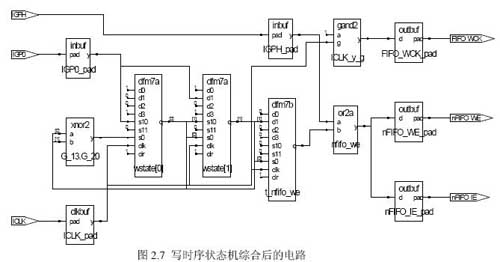

根据整个控制过程的逻辑和相应器件的读写时序,可以将整个FIFO 的控制过程分为写入控制和读出控制两个部分,在写入控制中用了4个有限状态机来实现,它们分别是IDLE,WEN0,WEN1,WEN2。根据状态机的图,采用硬件描述语言VHDL 实现了对CPLD 的逻辑的设计、综合和仿真。逻辑综合采用Synplicit7.2 公司专门针对CPLD/CPLD 的逻辑综合工具。该软件带有Altera公司的综合模块库,可以针对Altera公司的CPLD 器件对逻辑综合后的结果进行优化和改进,其中写状态机综合后的电路原理图为图2.7。

对于逻辑设计的仿真时序验证工作重要采用ALDEC 公司的仿真工具Active-HDL4.2,然后加入综合工具生成的标准时延文件(SDF文件),通过仿真结果的验证,说明CPLD 的逻辑设计是符合FIFO 读写控制模块的功能要求的。最后综合的逻辑结果通过Altera 公司的MAXplus10软件,采用ByteBlaster 电缆下载到CPLD 芯片中。

3. 实验结果:

图3.1 是采用QCIF(176× 144) 格式的视频图像,压缩编码算法采用M-JPEG2000标准。其中前一幅是无损压缩恢复的结果图,后一幅为有损压缩。相应的压缩编码指标如表3.1 所示。

图 3.1

从上面表3.1 的结果可以看出,整个压缩系统可以实现对视频图像的压缩编码。压缩后的视频流比较流畅。

从通过逻辑分析仪测得的时序图(图2.8、图2.9)可以看出,CPLD 实现的FIFO 控制信号满足视频AL422B的时序要求,整个视频数据传输的通路工作正常,基本上达到了系统设计的指标和要求。同时这种方案可以作为一个整体的视频采集模块,在一般的使用DSP 的EMIF 总线的情况下的都可以无需改动就可以作为一个采集模块直接使用,大大简化硬件电路开发的难度。此方案已经在基于DSP 的视频PCI 采集压缩卡中得到了验证,达到了很好的效果。本文的基于CPLD的视频采集通用模块已经在M-JPEG2000的视频采集压缩卡得到了应用。

- 基于DSP的多路音/视频采集处理系统设计(01-07)

- DVB-C视频传输接口ASI的实现(09-27)

- 用VHDL语言在CPLD上实现串行通信(10-13)

- 基于DSP和CPLD的智能相机系统设计与研制(08-19)

- 基于AD7892SQ和CPLD的数据采集系统的设计(11-10)

- 基于CPLD的异步ASI/SDI信号电复接光传输设备的设计(11-18)