基于DSP的多路音/视频采集处理系统设计

摘要: 采用TI公司的TMS320DM642型数字媒体数字信号处理器(DSP)设计多路音/视频采集处理系统,实现实时处理4路模拟视频和音频输入、1路模拟/数字视频和l路模拟音频信号输出的功能,该系统可适应PAL/NTSC标准复合视频CVBS或分量视频Y/C格式的模拟信号和标准麦克风或立体声音频模拟输入,具有PAL/NTSC标准S端子或数字RCB模拟/数字信号输出和标准立体声音频模拟输出。并给出软/硬件设计原理和电路。

关键词:TMS320DM642;图像采集处理;PAL/NTSC制式;数字信号处理器

l 引言

当前,在数字图像处理中,由于数据量大、算法难度高,因此实时性成为技术难点之一。如果采用专用电路实现,虽然实时性得到保证,但系统的灵活度大大降低。因此,寻求一种高速通用数字信号处理系统成为当务之急。

II公司推出的TMS320DM642(以下简称DM642)型数字信号处理器可实时处理4路模拟视频和音频输入、l路模拟/数字视频和1路模拟音频信号输出,适应PAL/NTSC标准复合视频CVBS或分量视频Y/C格式的模拟信号输入,可适应PAL/NTSC标准S端子或数字RGB模拟/数字信号输出,可适应标准麦克风或立体声音频模拟输入及标准立体声音频模拟输出,具有对多路采集数据进行实时处理和分析的功能,可实现数据和图像叠加显示。

2 DM642简介

DM642型数字信号处理器可采用500 MHz或600 MHz的工作频率,每秒最多可完成4.8 G次操作,具备在线编程功能,带有的丰富外围接口可以与多种存储器相连,可以直接与网络连接,是高速图像处理的优选器件。

DM642的CPU采用第二代VelociTI.2内核结构,含有双数据通路、8个运算单元,每周期可执行8条32-bit指令,支持4个16-bit和8个8-bit连乘加MAC指令,有64个寄存器,取数/存数的数据通道为64-bit。

DM642采用带2级存储器的完全存储器分层体系结构,2级存储器中的Cache控制器可以自动完成分层存储器体系结构的管理和调度,外部存储器访问和片上外设的访问通过EDMA完成。

DM642有3个视频输入输出口和多路音频信号的输入输出串口。外部存储器接口EMIF提供了64-bit宽度的外总线数据接口,支持与各种器件的无胶合接口。DM642还具有主机并行接口、外围设备互联口、多通道缓存串口和通用I/O端口。

3 系统功能与硬件电路设计

3.1 系统总体结构

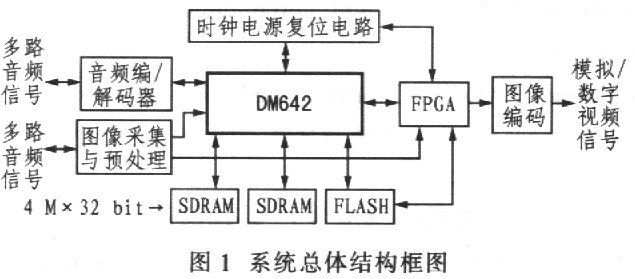

系统总体结构如图1所示,图像采集和预处理单元主要完成图像信号的输入,具有多路信号复用功能,对输入的模拟视频信号进行数字化及格式的转变。FPGA控制系统的逻辑和图像数据的流向,并且可对DM642输出的图像数据进行加工,进而输出到图像编码单元。图像处理单元采用DM642进行高速数据处理和分析。图像编码单元对图像数据进行编码,形成标准的模拟视频信号,可以直接输出到显示设备上。

对于4路视频和4路音频信号,CPU在1个时刻只能处理1路数据,DM642片外位于EMIF的CEO地址空间扩展了2个4 Mx32 bit的SDRAM,可分别存放图像采集数据和图像处理数据,以提高数据采集和存储速度。

3.2 视频口接口设计

DM642有3个视频口,每个都可以配置为上下2个通道,但2个通道必须同时为视频输入口或输出口。结合实际应用,DM642带了4路模拟视频输入(cif格式,分辨率为352×288)和1路模拟视频输出。

VPO A通道配置为8-bit BT.656视频输入或输出口,接第一通道视频输入或视频输出。VPl A通道配置为8-bit BT.656视频输入口,接第二通道视频输入。VP2 A和B通道配置为2个8-bit BT.656视频输入口,接第三和第四通道视频输入。VP0和VPI的B通道配置为MCASP,接4个音频Codec。

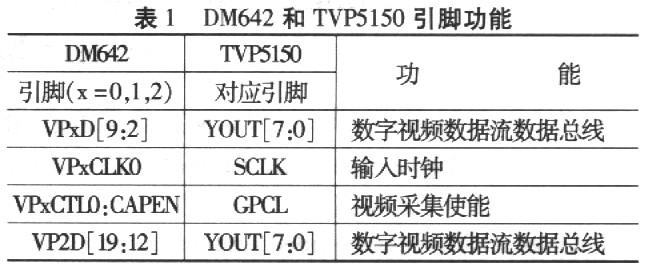

TVP5150型视频编码器支持PAL/NTSC、CVBS或Y/C模拟视频输入,8-bit BT.656数字视频数据流输出。SAA7105型视频解码器支持8-bit BT.656数字视频数据流输入,PAL/NTSC CVBS或Y/C模拟视频输出。通过DM642的I2C总线对视频编/解码器的内部寄存器进行编程,实现不同的输入输出。DM642和TVP5150的对应引脚功能见表1。

视频编解码器的参数通过I2C总线配置,由于TVP5150的I2C从地址只有2种选择,因此需要用CBT3257型2选l转换开关来切换。

作为视频输入口时,视频数据的行/场同步又包含BT.656数字视频数据流中的EAV和SAV时基信号控制,视频口只需视频采样时钟和采样使能信号(控制采样起始),TVP5150用系统时钟SCLK提供采样时钟,用可编程引脚GPCL提供采样使能。作为视频输出口时,视频口要为SAA7105提供时钟和行/场同步信号。

在视频输出电路中,J1、J2、J3可配置成RGB输出信号,J2、J3可连接S端子,J1、J2、J3、J4、J5可直接输出到电脑的显示器上。具体接口电路如图2和图3所示。DM642与SAA7105的对应引脚功能见表2所列。

- 全面解读 嵌入式DSP上的视频编解码(08-19)

- 基于ADSP-TS201S的图像采集处理系统(08-12)

- 基于Blackfin533的H.264编码(08-18)

- 图形液晶显示模块在嵌入式系统中的应用(09-02)

- 基于DSP和FPGA的电视观瞄系统设计(09-02)

- TI手提多媒体设备解决方案(09-23)