基于DSP的多路音/视频采集处理系统设计

3.3 多通道音频串口的接口设计

笔者采用了4路模拟音频输入和1路模拟音频输出,采用TLV320AIC23B型音频编/解码器,它支持麦克风/立体声模拟输入/输出和数字音频数据流输出/输入。

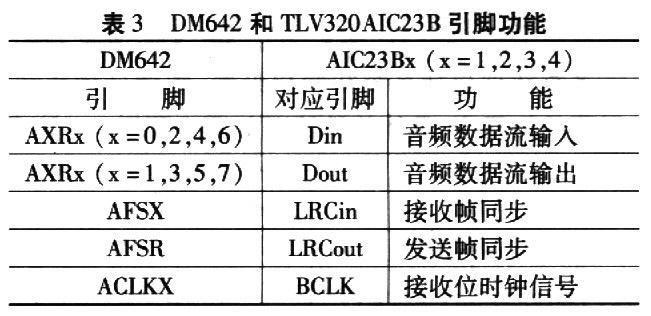

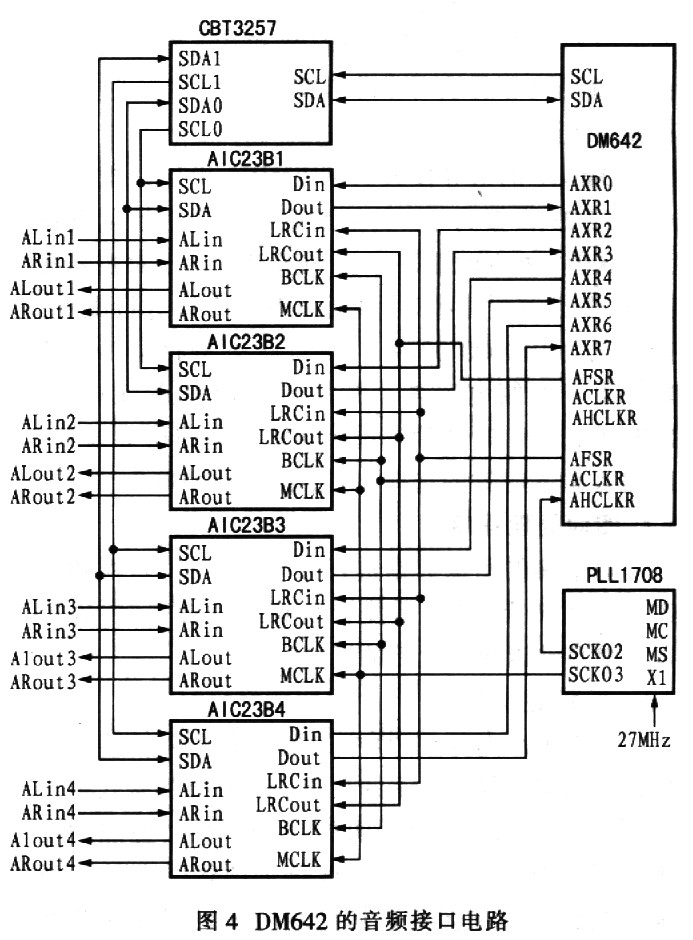

PLLl708型可编程视频/音频同步数字锁相环给McASP和TLV320AIC23B提供时钟信号,SCK02端口接McASP的AHCLKX,SCK03端口接TLV320AIC23B的主时钟MCLK。PLLl708的时钟输入为27 MHz。DM642与TLV320AIC23B的对应引脚功能见表3。

AIC23B数据口配置为从,McASP的8个收/发引脚配置为4收/4发,分别接4个编解码器的Dout/Din。McASP的接收帧同步配置为输出,同时给4个编解码器的LRCout。McASP的发送帧同步配置为输出,同时给4个编解码器的LRCin。McASP的发送位时钟ACLKX配置为输出(由AHCLKX分频),同时给4个编解码器的BCLK。AIC23B的控制口配置为I2C,由CBT3257型2选1开关来切换。具体电路如图4所示。

另外,给DM642供电时应注意CPU的上电次序:CHU内核应先于I/O上电,后于I/O掉电,CPU内核与I/0应尽可能同时供电,二者的时差不能太大(<1 s),否则会影响器件的寿命或损坏器件。用可编程时钟电路可很好地解决整个电路的时钟问题。

4 系统软件设计

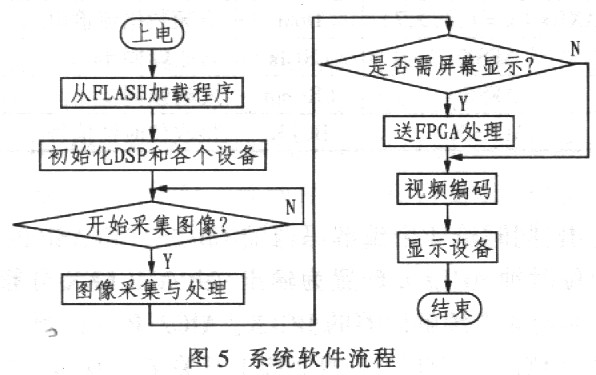

系统软件包括系统初始化设置、图像处理算法和屏幕叠加程序,具体软件流程如图5所示。

4.1 系统初始化设置程序

对整个硬件系统进行初始化,其中包括DM642的上电初始化、DM642的寄存器和系统配置引脚的设置、利用I2C总线对TVP5150和SAA7105进行寄存器设置。

DM642的引导模式为从EMIFA引导,把引脚AEA[22:21]设置为ll,其他配置引脚的初始化设置为默认值。外围配置寄存器(PERCFG)用于对控制视频口、多通道缓冲串口、多通道音频串口进行配置,初始化为0x0000 0079h。设备状态寄存器(DEVS-TAT)用于控制电路各个外围设备的状态:EMAC、HPI、PCI、CPU时钟频率选择模式、电路引导模式、EMIFA输入时钟的选择,初始化为0x0000 005Ch。

4.2 图像处理程序

对采集的图像数据进行处理和分析,对视频流进行格式转换,可以是复合视频或分量视频,也可以压缩存储以便于此后的浏览。

4.3 屏幕叠加程序

把FPGA内部FIFO中的数据和视频口输出的数据混和完成屏幕显示的功能。屏幕叠加有几种方式,背景为透明的、半透明的、不透明的,叠加的位置也可任意设置,只需修改叠加图像的起始点坐标,把相应的图像信息加到对应的视频图像队列中。

4.4 视/音频信号采集存储与图像数据读取程序

对于4路视频信号和4路音频信号,CPU在1个时刻只能处理1路数据,因此在DM642片外扩展了2个4Mx32bit的SDRAM,在系统工作的任一时刻,一个用于图像的采集,采集部分向该存储区写图像数据,另一个用于外部对图像数据的读取,DSP可以读取该存储区中的图像数据。双SDRAM结构的重要特点是DSP对存储区的数据操作是来回切换的。当A/D转换数据写满SDRAM-l时,FPGA会向DSP发出中断信号,此时,在DSP读取SDRAM-l中数据的同时,A/D转换数据写入SDRAM-2,当SDRAM-2中的数据写满时,FPGA向DSP发出中断信号,此时DSP读取SDRAM-2中的数据,同时,A/D转换数据写入SDRAM-l,如此交替,实现数据的写入与读取同时进行。由于DSP读取SDRAM中数据的速度远远大于A/D转换写入数据的速度,因而允许采集与外部访问同时进行,采用2个存储区操作的乒乓式切换满足数据实时交换的要求。

由于DSP对存储区的数据操作是来回切换的,因此需要采用中断来实现取数。具体实现是在DSP内部设置中断,这里选用INT6作为中断触发引脚。当外部中断信号到来时,则相应中断服务程序执行中断响应。

5 结束语

本系统能够同时处理4路CIF格式的数字视频,并且可以动态切换,总采样速率可达100帧/秒,每路速率为25帧/秒,可以完全保证图像实时采集。

对图像的叠加有多种方法,叠加的位置也可通过修改叠加图像的起始点坐标来进行任意设置。DM642还具有网络接口,可以对输出的视频信号进行压缩并由网络实时传输。

基于DM642的图像采集处理系统能广泛应用于机顶盒、IP可视电话、网络视频会议等领域。

- 全面解读 嵌入式DSP上的视频编解码(08-19)

- 基于ADSP-TS201S的图像采集处理系统(08-12)

- 基于Blackfin533的H.264编码(08-18)

- 图形液晶显示模块在嵌入式系统中的应用(09-02)

- 基于DSP和FPGA的电视观瞄系统设计(09-02)

- TI手提多媒体设备解决方案(09-23)