基于CPLD控制的通用视频采集模块

1. 引言

对于用于视频图像处理的DSP 来说,由于前端的A/D 采集速度较低,一般为了减少DSP 的开销,在视频采集A/D 和DSP之间接入先进先出存储器(FIFO) 作为缓冲。

基于先进先出存储器(FIFO) 的多样性,一般在视频采集与微处理器模块之间很少提供无缝接口。传统的方法是用简单的逻辑电路实现很少一部分接口控制,大多数是通过软件来实现,虽然软件设计灵活性比较大,但是对软件设计者提出很高的要求; 一般来说使用的都是线存的FIFO,这种FIFO 的存储量比较少,会花费CPU 很大的开销。

本文实现了一种在采集A/D 模块、专用视频FIFO 以及DSP 微处理使用CPLD 作为纯硬件控制的方案。使用这种方案的创新点是首先因为使用的是帧存储器FIFO,存储一帧或者一场视频数据,这样可以大大减轻DSP的开销,提高DSP 的效率,从而更好的提高视频处理的实时性;其次因为接口逻辑比较复杂,一般用软件实现起来比较困难,使用可编程CPLD实现全部的硬件接口逻辑,减少软件设计的难度,减少DSP 的开销。同时可以发挥CPLD 现场可编程的特点,可以像软件一样更改; 最后可

以作为一个集成的通用硬件采集模块。

本文实现的是基于TI TMS320C6x 的DSP的视频采集压缩卡的A/D采集模块以及接口控制模块。在采集模块主要功能是将从CCD 摄像头输入的模拟视频信号转换为数字信号,普通CCD摄像头的输出是NTSC 制式的复合全电视信号CVBS 信号,通过SAA7114H TV解码芯片将模拟TV 信号解码,转换为符合ITU-R BT.601 标准的数字视频信号,并且由CPLD 控制模块将数据存储到专用的视频FIFO芯片,中断DSP 读取数据处理。

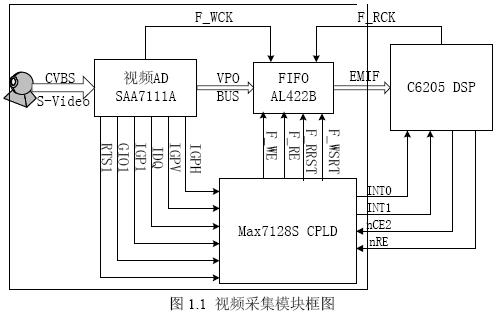

具体的信号控制见图1.1。

2. 模块介绍

2.1. 视频采集模块

采集模块采用PHILIPS 公司的视频A/D 芯片SAA7114H,该专用视频A/D 具有6 路模拟视频输入,两个模拟预处理通道,并且抗混滤波、梳状滤波都被集成到芯片内部,这样对于硬件设计带来了极大的方便。同时场同步信号IGPV,行同步信号IGPH,有效图像数据输出信号IDQ,时钟输出信号ICLK都有管脚直接引出,这样省去了以往的时钟同步电路的设计,可靠性也有所提高。系统内部锁相环技术的集成使得可靠性和设计复杂度都有极大的降低。SAA7114H 的配置支持I2C,可以通过DSP的通用I/O 口软件模拟I2C总线。

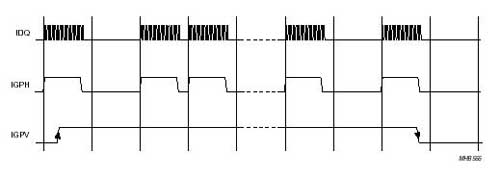

从图2可以看出整个过程是在ICLK在上升沿触发,在 IDQ 有效的情况下传输的数据有效,数据输出的格式为(下为奇数场的一行数据扫描)

FF00 0080 U0Y0,V0Y1,U1Y2,V1Y3,…………,U319Y638,V320Y639

其中FF00 和0080 是奇数场标志位。

当输出IGPH 有效表明为一行数据的扫描,当IGPH无效的情况下,表明数据在回扫。从图3可以看出当IGPV 有效说明是一场数据的扫描,当为无效时,说明为一场数据结束。通过这几个状态信号的输出,以及其它标志信号可以对行数据和场数据同步进行控制。具体见图2.1(信号一行扫描输出状态) 和图2.2(信号一场扫描输出状态)。

图2.1 信号输出状态( 一行扫描)

图2.2 信号输出状态( 一场扫描)

2.2. 视频缓冲模块FIFO

AL422B 是Averlogic 公司的专用视频的FIFO,最大存储为384K× 8bits,同时支持VGA,CCIR,NTSC,PAL 等视频制式,两端独立的读写操作,支持不同速率的读写。根据CCIR.601协议,一场图像数字化后最大的数据量是220K× 16bit,因此,采用的AL422B 足够可以容纳完整的一场视频图像的数据量。采用这种大的FIFO 的设计可以降低DSP 对视频FIFO 读写控制时序的复杂度,使整个视频图像处理流程简捷,同时减少控制信号。

2.3. CPLD控制模块

该模块的组成主要是一片Altera 公司的CPLD 芯片EPM7128STC100,其主要功能是提供DSP 的EMIF 接口与视频FIFO 相连时所需的一些额外的辅助逻辑(glue logic)。另外一个重要的功能是通过检测SAA7114H 输出的同步信号来生成DSP 中断,通知DSP 读取视频FIFO 中已满的一场图像数据。(视频FIFO AL422B 的容量为384K× 8bits,系统中使用两片并联成16bits的接口宽度,整个视频FIFO可以一次存放一帧的视频数据。)

CPLD通过SAA7114H的输出状态信号以及TMS320C6x DSP的相应输出控制信号生成FIFOAL422B 的控制信号。具体为:

根据SAA7114H输出的VPO 总线同步信号,控制将输出的数字视频信号写入到FIFO 中。

检查到SAA7114H输出的场同步信号后(表明FIFO 中已经存满一场图像数据),向DSP 发出INT 信号,通知其开始读取FIFO 中的图像数据。同时将FIFO 的写入指针复位到地址0x0000处。

根据SAA7114H 的两个输出信号IGP1 和RTS1,判定当前视频AD输出的视频数据是奇数场还是偶数场,同时发出不同的INT中断来通知DSP。

控制DSP 读取FIFO 中图像数据的读写时序,当读完一场数据后,将FIFO 的读出指针复位到地址0x0000 处。

控制FIFO 的写时钟与读时钟,并且使得写时钟与SAA7114H的输出时钟保持同步,使得读时钟与DSP 的外部分频后的时钟保持同步。

图2.4 FIFO 写时序控制

- 基于DSP的多路音/视频采集处理系统设计(01-07)

- DVB-C视频传输接口ASI的实现(09-27)

- 用VHDL语言在CPLD上实现串行通信(10-13)

- 基于DSP和CPLD的智能相机系统设计与研制(08-19)

- 基于AD7892SQ和CPLD的数据采集系统的设计(11-10)

- 基于CPLD的异步ASI/SDI信号电复接光传输设备的设计(11-18)